ADVANCED POWER ELECTRONICS CONVERTERS

#### **IEEE Press**

445 Hoes Lane Piscataway, NJ 08854

#### IEEE Press Editorial Board

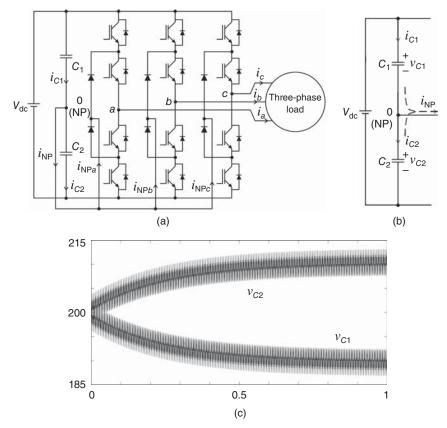

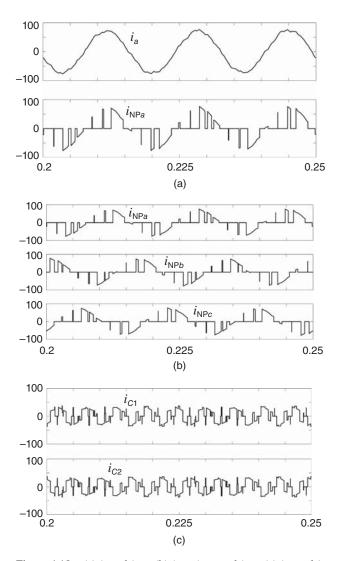

Tariq Samad, Editor in Chief

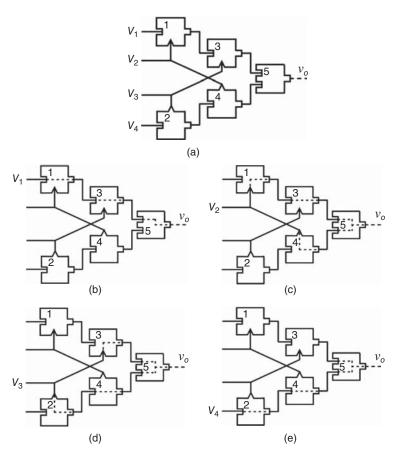

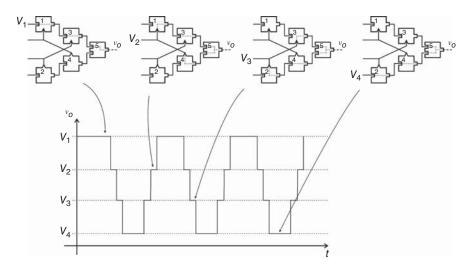

George W. Arnold Dmitry Goldgof Ekram Hossain Mary Lanzerotti Pui-In Mak Ray Perez Linda Shafer MengChu Zhou George Zobrist

Kenneth Moore, Director of IEEE Book and Information Services (BIS)

Technical Reviewers Marcelo Godoy Simões, Colorado School of Mines Hamid A. Toliyat, Texas A&M University

# ADVANCED POWER ELECTRONICS CONVERTERS PWM Converters Processing AC Voltages

## EUZELI CIPRIANO DOS SANTOS JR. EDISON ROBERTO CABRAL DA SILVA

Copyright © 2015 by The Institute of Electrical and Electronics Engineers, Inc.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. All rights reserved Published simultaneously in Canada

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at www.wiley.com.

#### Library of Congress Cataloging-in-Publication Data is available.

#### ISBN: 9781118880944

Printed in the United States of America

# CONTENTS

| PREFACE           |                                                                | xi |

|-------------------|----------------------------------------------------------------|----|

| CHAP              | TER 1 INTRODUCTION                                             | 1  |

| 1.1               | Introduction 1                                                 |    |

| 1.2               | Background 3                                                   |    |

| 1.3               | History of Power Switches and Power Converters 4               |    |

| 1.4               | Applications of Power Electronics Converters 6                 |    |

| 1.5               | Summary 9                                                      |    |

|                   | References 9                                                   |    |

| CHAP <sup>®</sup> | TER 2 POWER SWITCHES AND OVERVIEW OF BASIC POWER<br>CONVERTERS | 10 |

|                   | CONVERTERS                                                     | 10 |

| 2.1               | Introduction 10                                                |    |

| 2.2               | Power Electronics Devices as Ideal Switches 11                 |    |

|                   | 2.2.1 Static Characteristics 12                                |    |

|                   | 2.2.2 Dynamic Characteristics 12                               |    |

| 2.3               | Main Real Power Semiconductor Devices 16                       |    |

|                   | 2.3.1 Spontaneous Conduction/Spontaneous Blocking 17           |    |

|                   | 2.3.2 Controlled Conduction/Spontaneous Blocking Devices 18    |    |

|                   | 2.3.3 Controlled Conduction/Controlled Blocking Devices 19     |    |

|                   | 2.3.4 Spontaneous Conduction/Controlled Blocking Devices 22    |    |

|                   | 2.3.5 List of Inventors of the Major Power Switches 24         |    |

| 2.4               | Basic Converters 25                                            |    |

|                   | 2.4.1  dc-dc Conversion <b>28</b>                              |    |

|                   | 2.4.2 dc-ac Conversion 33                                      |    |

|                   | 2.4.3 ac-dc Conversion $43$                                    |    |

| 2.5               | 2.4.4 ac-dc Conversion 49<br>Summary 50                        |    |

| 2.5               | Summary 50<br>References 52                                    |    |

|                   | Keleielices 52                                                 |    |

| CHAP <sup>.</sup> | TER 3 POWER ELECTRONICS CONVERTERS PROCESSING ac               |    |

|                   | VOLTAGE AND POWER BLOCKS GEOMETRY                              | 56 |

| 3.1               | Introduction 56                                                |    |

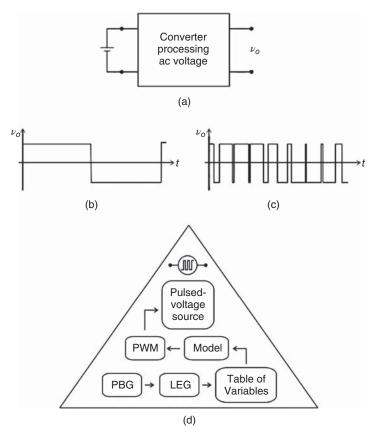

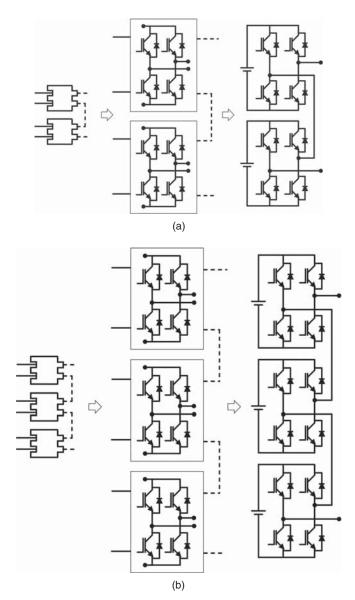

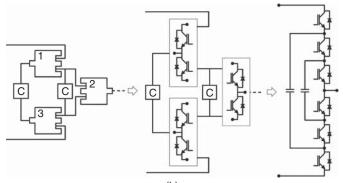

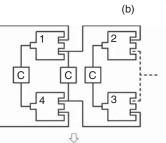

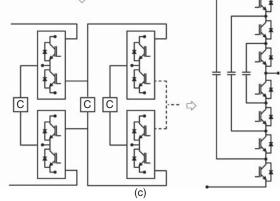

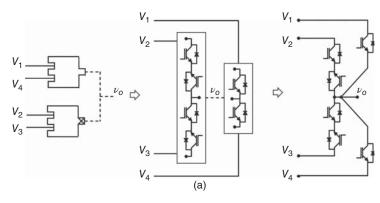

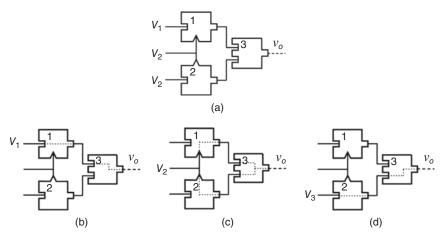

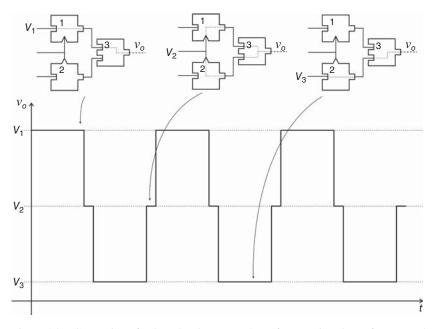

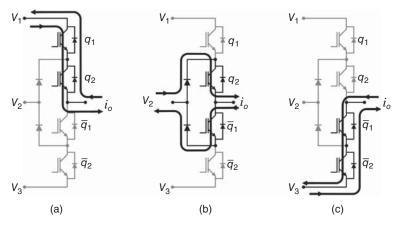

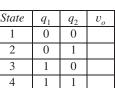

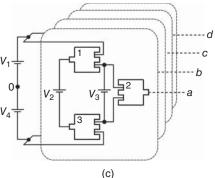

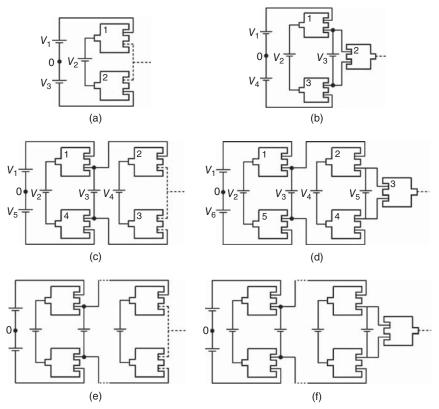

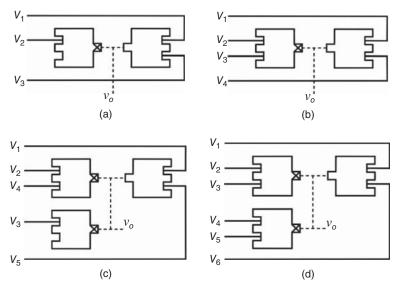

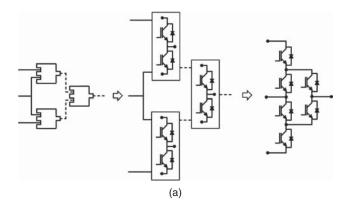

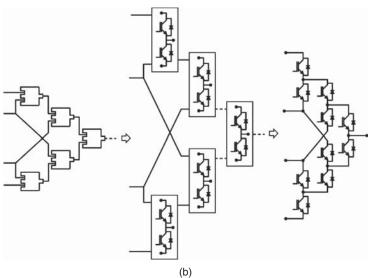

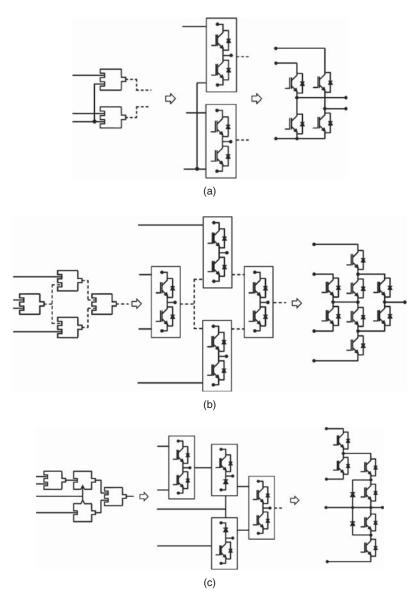

| 3.1<br>3.2        | Principles of Power Blocks Geometry (PBG) 58                   |    |

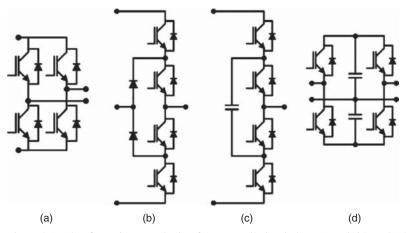

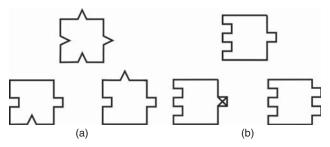

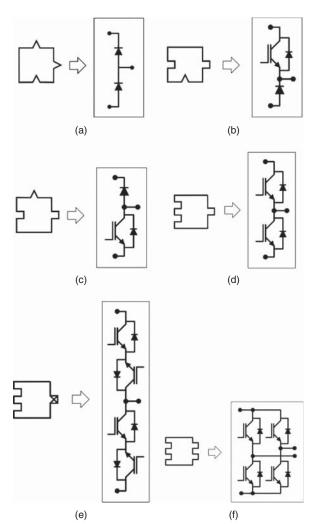

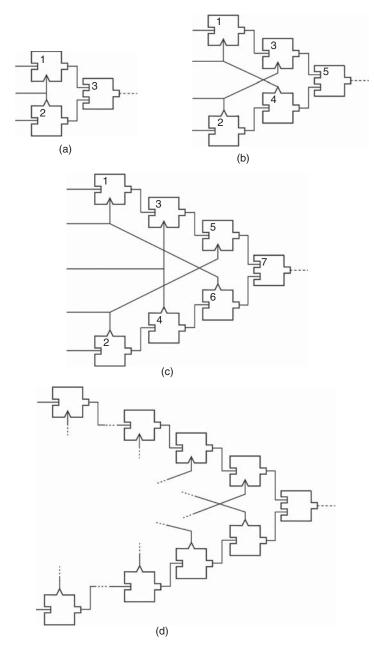

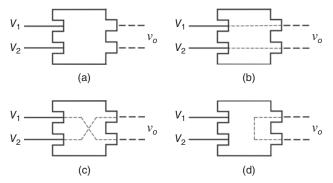

| 3.2<br>3.3        | Description of Power Blocks 62                                 |    |

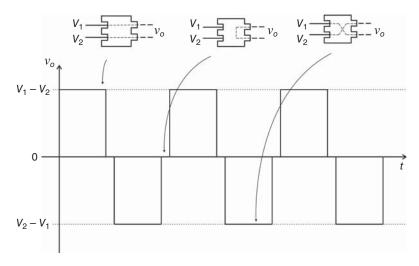

| 3.4               | Application of PBG in Multilevel Configurations 67             |    |

| 5.1               | 3.4.1 Neutral-Point-Clamped Configuration 68                   |    |

|                   |                                                                |    |

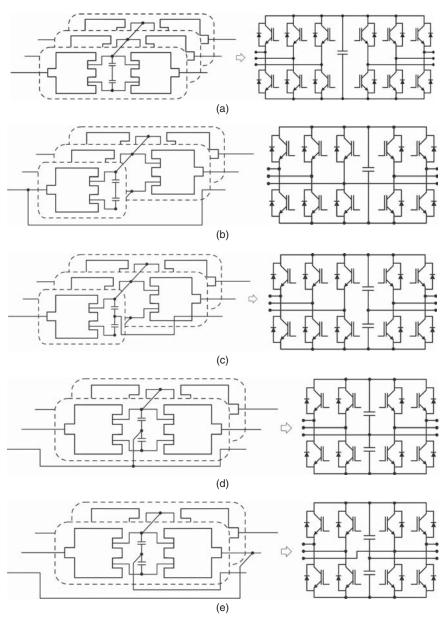

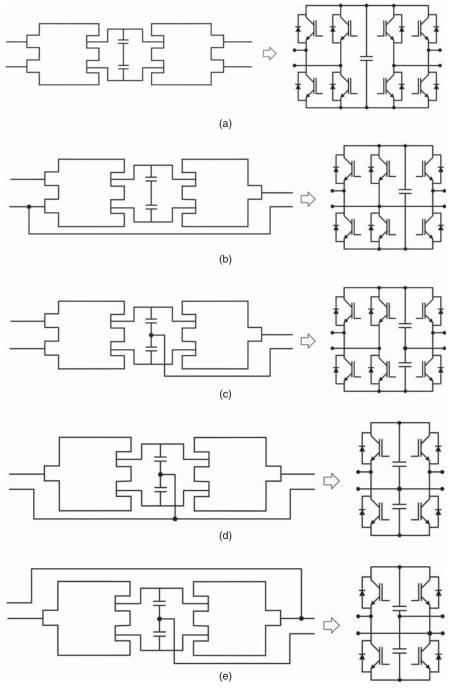

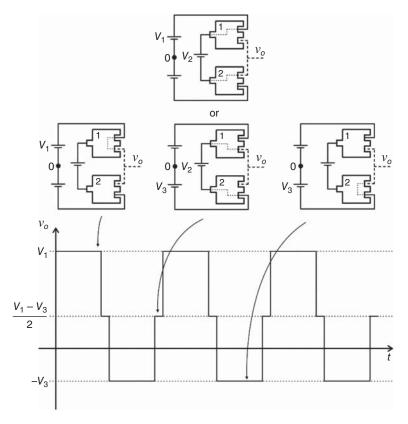

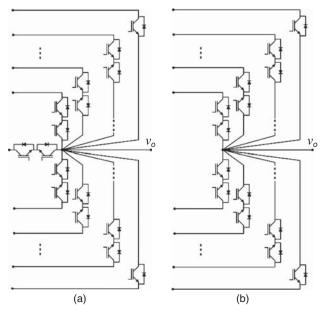

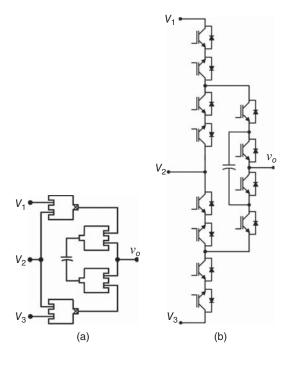

- 3.4.2 Cascade Configuration 72

- 3.4.3 Flying Capacitor Configuration **75**

- 3.4.4 Other Multilevel Configurations **79**

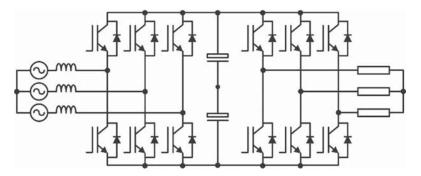

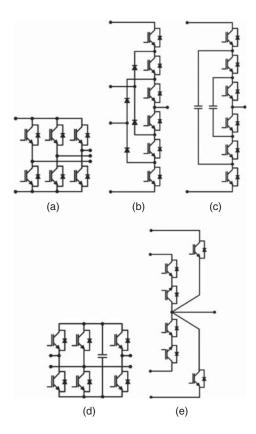

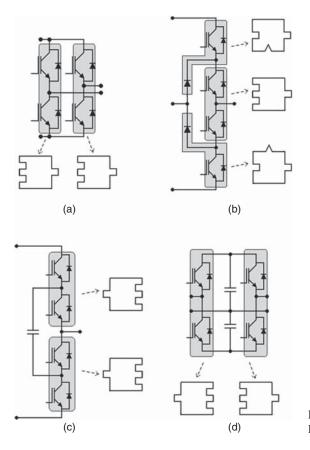

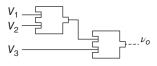

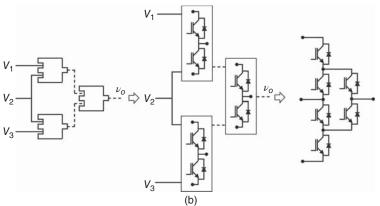

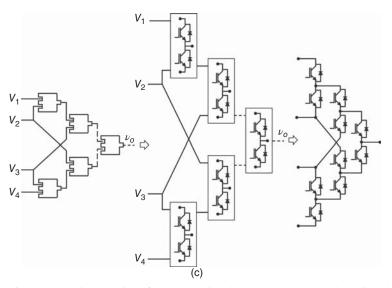

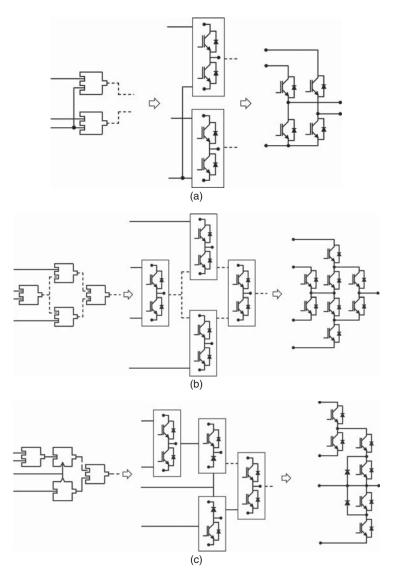

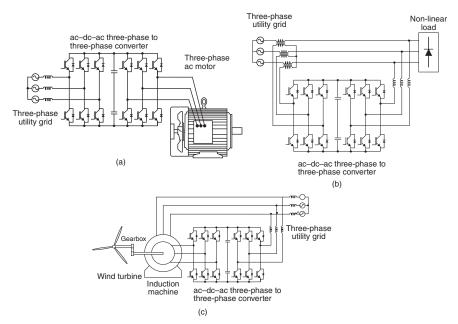

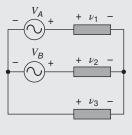

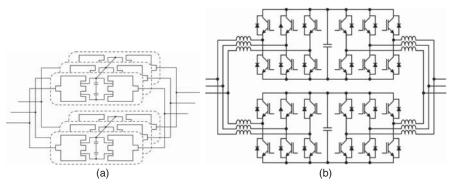

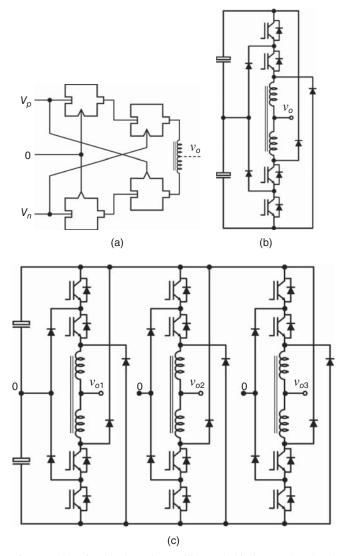

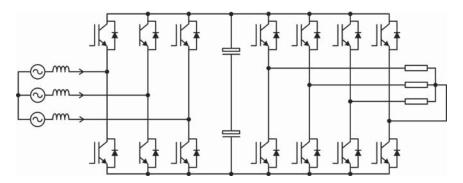

- 3.5 Application of PBG in ac-dc-ac Configurations 81

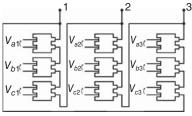

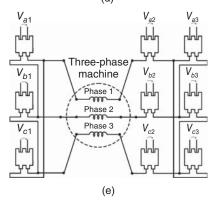

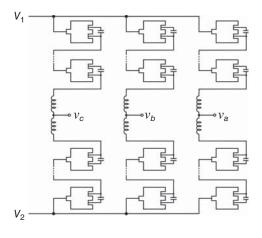

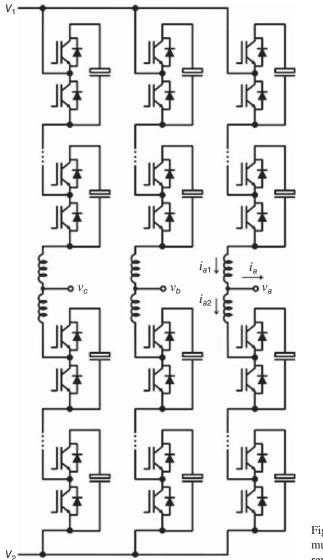

- 3.5.1 Three-Phase to Three-Phase Configurations 82

- 3.5.2 Single-Phase to Single-Phase Configurations **85**

88

125

3.6 Summary 85 References 87

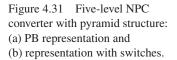

#### CHAPTER 4 NEUTRAL-POINT-CLAMPED CONFIGURATION

- 4.1 Introduction 88

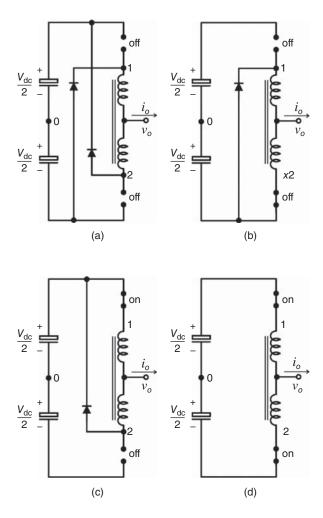

- 4.2 Three-Level Configuration 89

- 4.3 PWM Implementation (Half-Bridge Topology) 93

- 4.4 Full-Bridge Topologies 95

- 4.5 Three-Phase NPC Converter 98

- 4.6 Nonconventional Arrangements by Using Three-Level Legs 101

- 4.7 Unbalanced Capacitor Voltage 108

- 4.8 Four-Level Configuration 112

- 4.9 PWM Implementation (Four-Level Configuration) 115

- 4.10 Full-Bridge and Other Circuits (Four-Level Configuration) 118

- 4.11 Five-Level Configuration 119

- 4.12 Summary **124** References **124**

#### CHAPTER 5 CASCADE CONFIGURATION

| CHAPTER 6 FLYING-CAPACITOR CONFIGURATION 17 |                                                                |  |

|---------------------------------------------|----------------------------------------------------------------|--|

|                                             |                                                                |  |

|                                             | References 170                                                 |  |

| 5.11                                        | Summary 169                                                    |  |

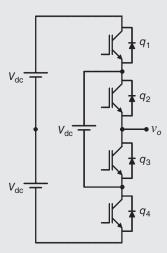

| 5.10                                        | Four H-Bridge Converters and Generalization 169                |  |

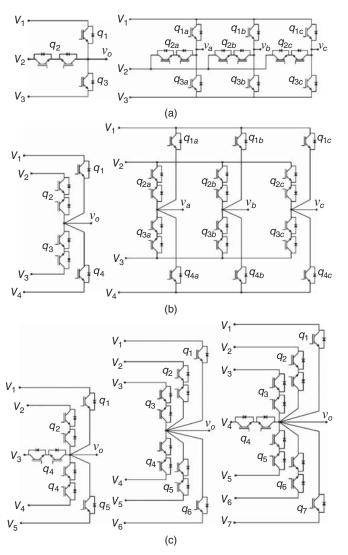

| 5.9                                         | Three H-Bridge Converters 164                                  |  |

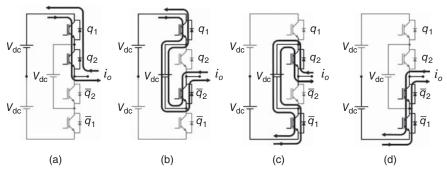

| 5.8                                         | Two H-Bridge Converters (Seven- and Nine-Level Topologies) 162 |  |

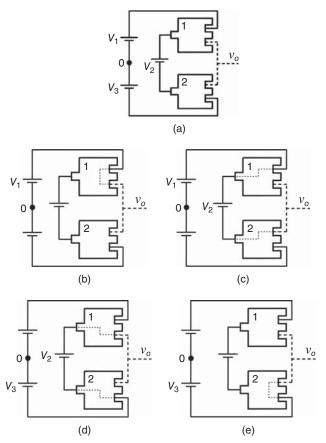

| 5.7                                         | Three-Phase Converter—Two Cascade H-Bridges Per Phase 149      |  |

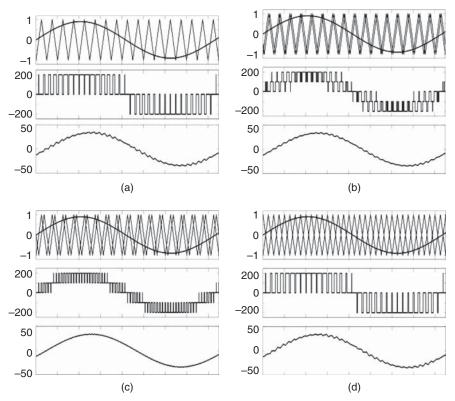

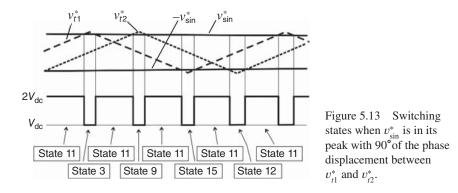

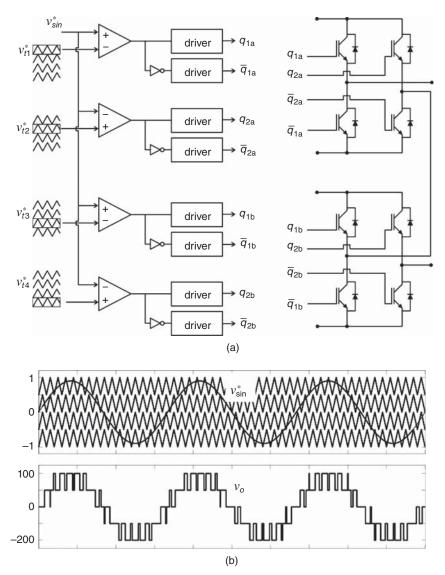

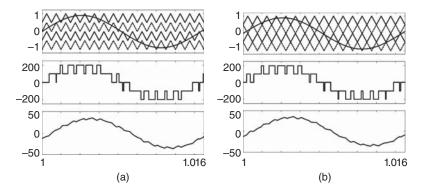

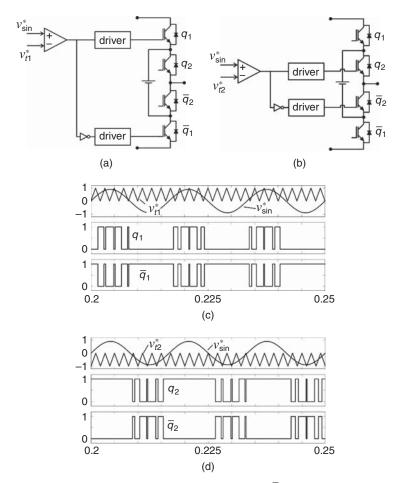

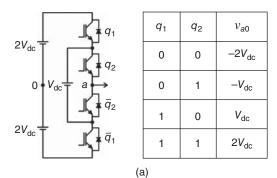

| 5.6                                         | PWM Implementation of Two Cascade H-Bridges 146                |  |

| 5.5                                         | Two H-Bridge Converters 144                                    |  |

| 5.4                                         | Three-Phase Converter—One H-Bridge Converter Per Phase 140     |  |

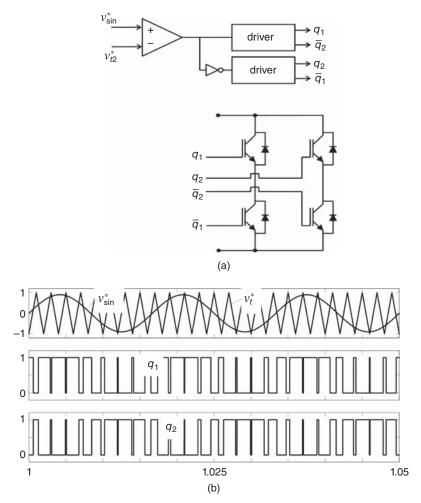

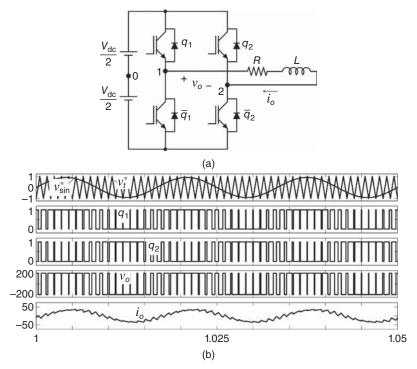

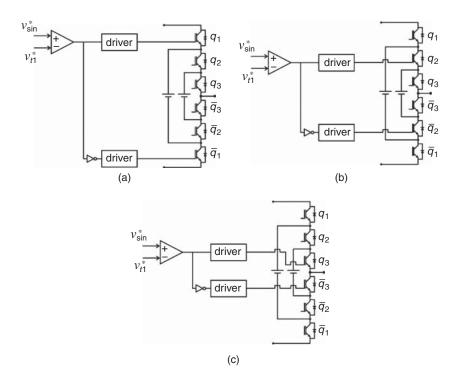

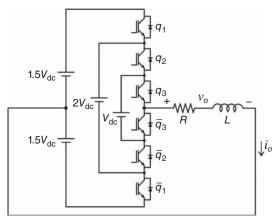

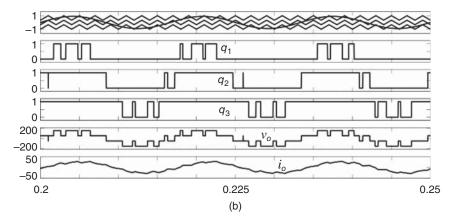

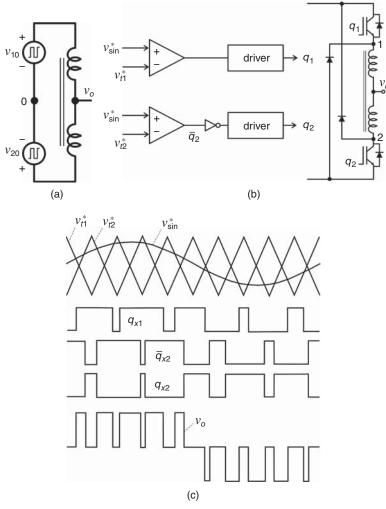

| 5.3                                         | PWM Implementation of A Single H-Bridge Converter 129          |  |

| 5.2                                         | Single H-Bridge Converter 126                                  |  |

| 5.1                                         | Introduction 125                                               |  |

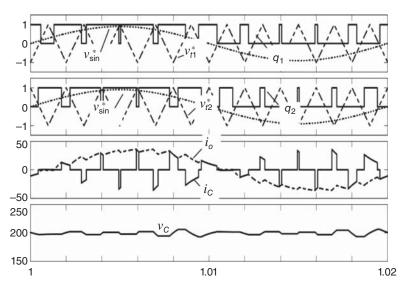

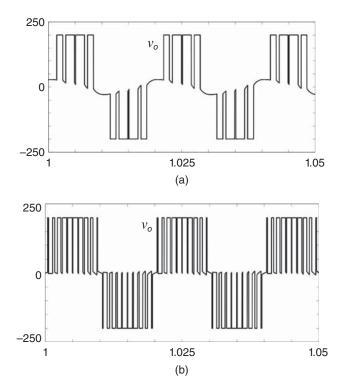

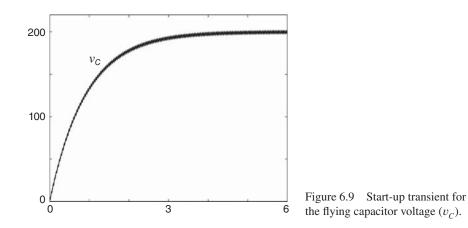

- 6.2 Three-Level Configuration 173

- 6.3 PWM Implementation (Half-Bridge Topology) 177

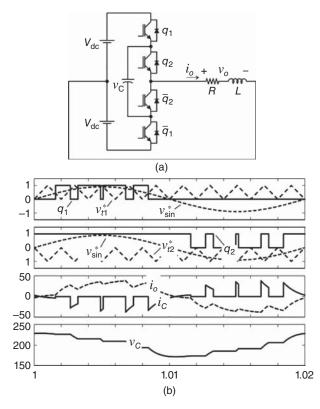

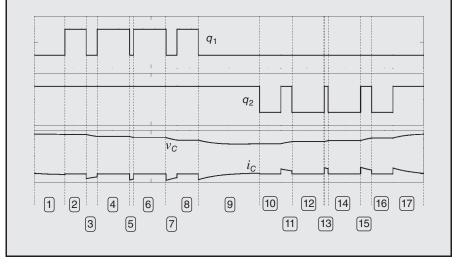

- 6.4 Flying Capacitor Voltage Control 179

- 6.5 Full-Bridge Topology 181

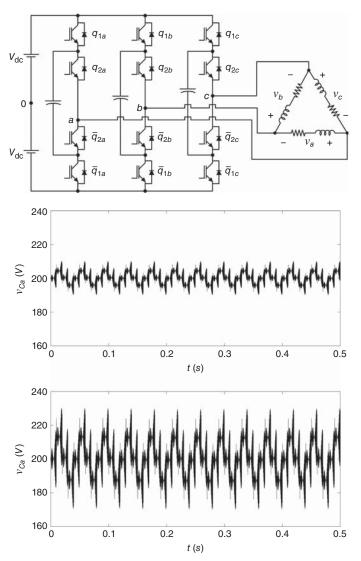

- 6.6 Three-Phase FC Converter **183**

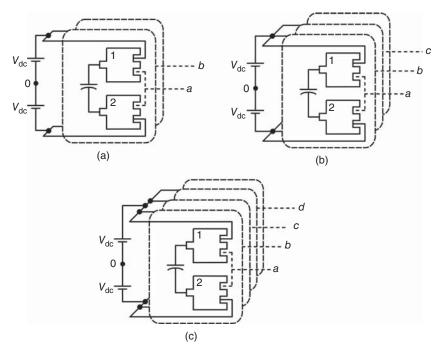

- 6.7 Nonconventional FC Converters with Three-Level Legs 186

199

221

- 6.8 Four-Level Configuration 189

- 6.9 Generalization 196

- 6.10 Summary **197** References **198**

#### CHAPTER 7 OTHER MULTILEVEL CONFIGURATIONS

- 7.1 Introduction 199

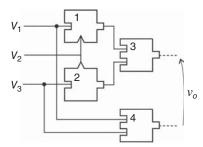

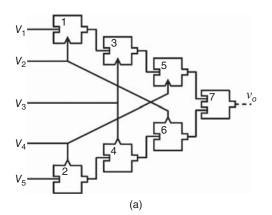

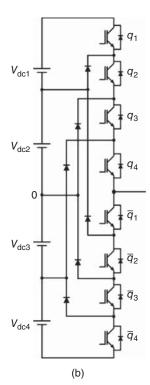

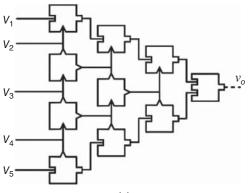

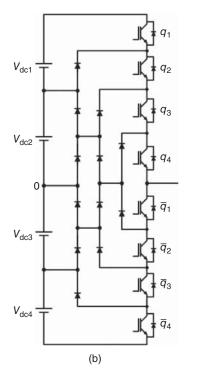

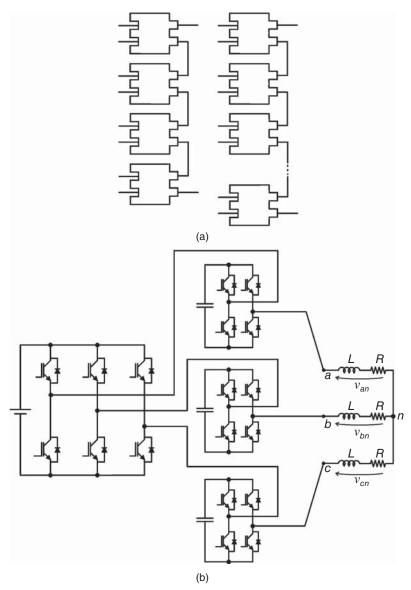

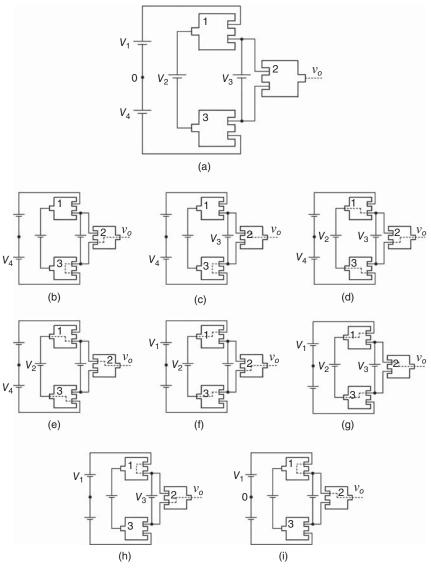

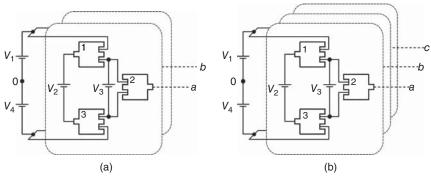

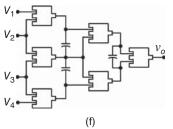

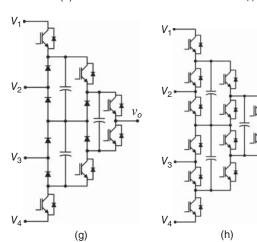

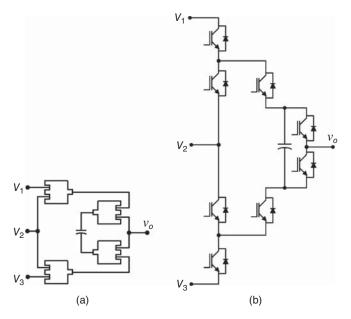

- 7.2 Nested Configuration 200

- 7.3 Topology with Magnetic Element at the Output 205

- 7.4 Active-Neutral-Point-Clamped Converters 211

- 7.5 More Multilevel Converters 214

- 7.6 Summary 218 References 219

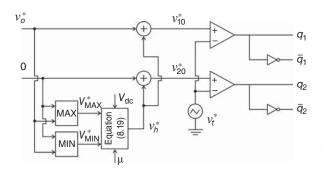

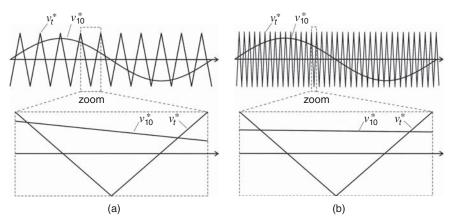

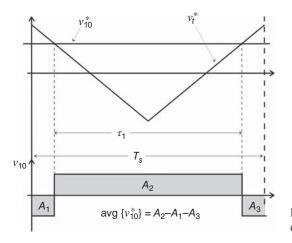

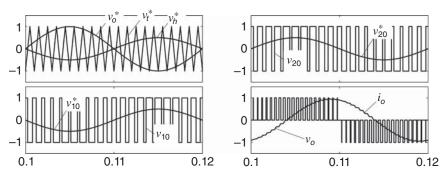

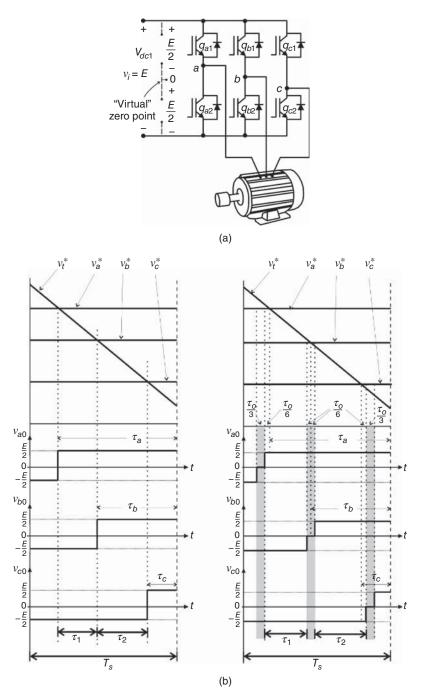

#### CHAPTER 8 OPTIMIZED PWM APPROACH

- 8.1 Introduction 221

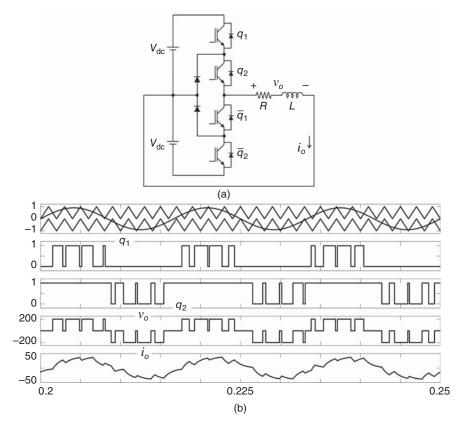

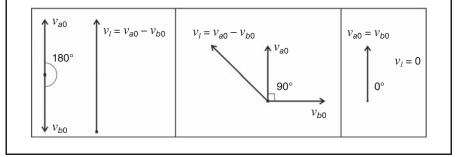

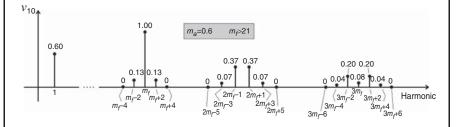

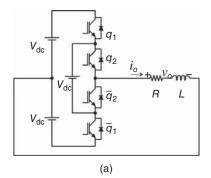

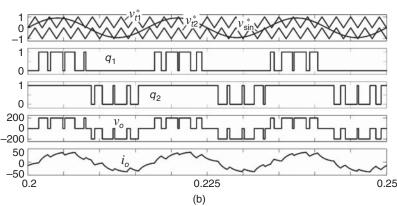

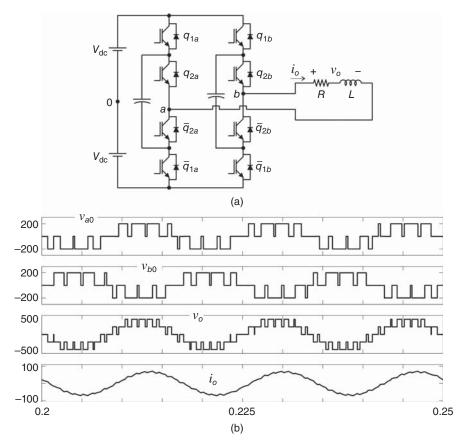

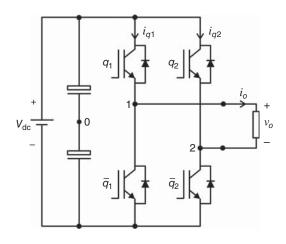

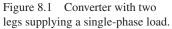

- 8.2 Two-Leg Converter 222

- 8.2.1 Model 222

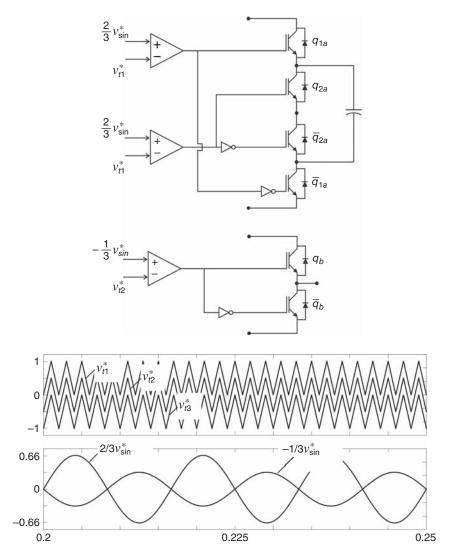

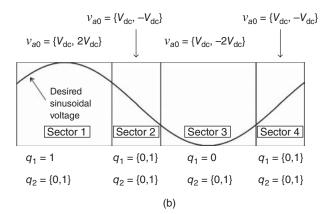

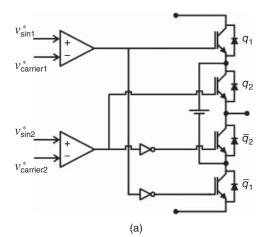

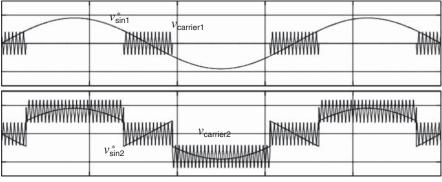

- 8.2.2 PWM Implementation 223

- 8.2.3 Analog and Digital Implementation 228

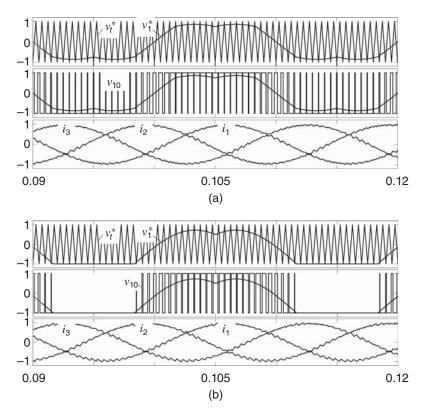

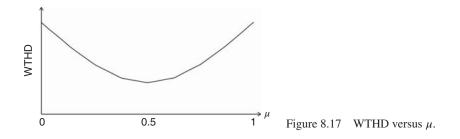

- 8.2.4 Influence of  $\mu$  for PWM Implementation 231

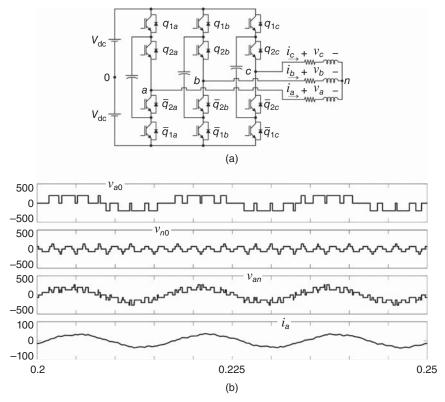

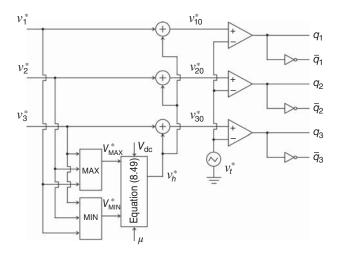

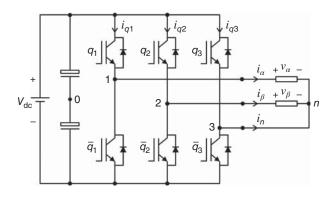

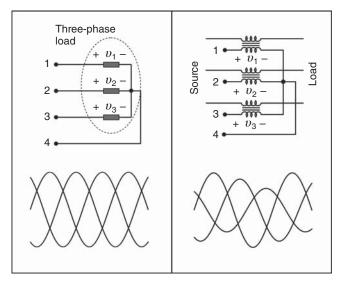

- 8.3 Three-Leg Converter and Three-Phase Load 233

- 8.3.1 Model 233

- 8.3.2 PWM Implementation 235

- 8.3.3 Analog and Digital Implementation 236

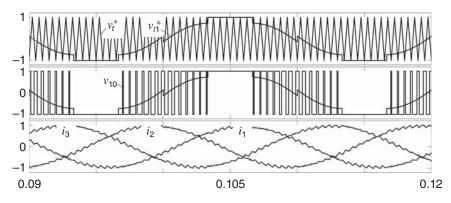

- 8.3.4 Influence of  $\mu$  for PWM Implementation in a Three-Leg Converter 236

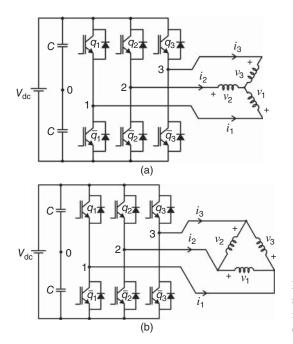

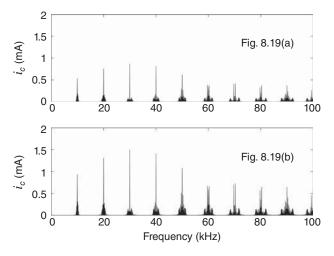

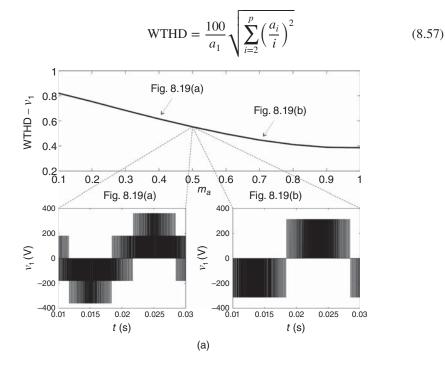

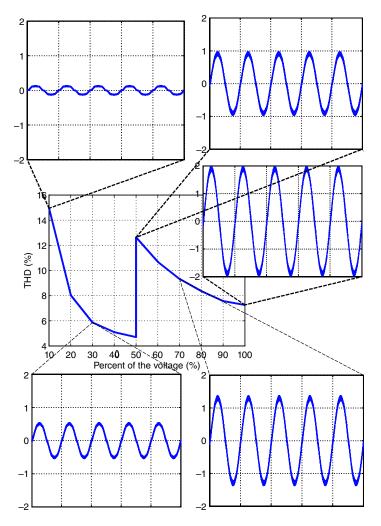

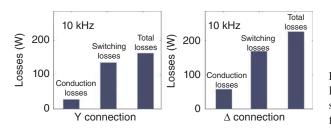

- 8.3.5 Influence of the Three-Phase Machine Connection over Inverter Variables 238

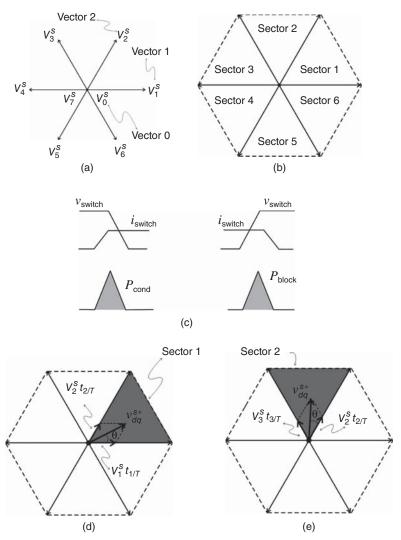

- 8.4 Space Vector Modulation (SVPWM) 243

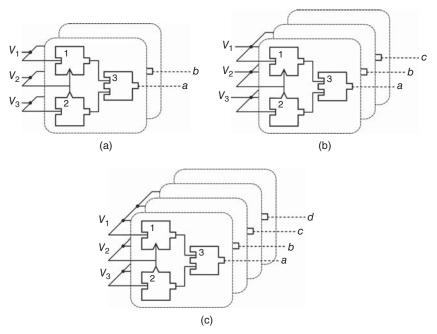

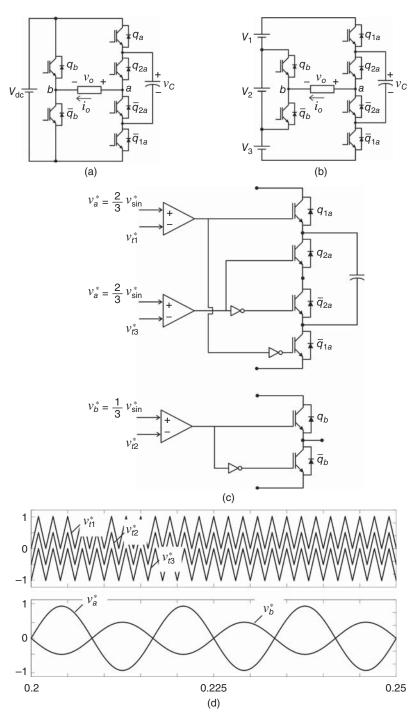

- 8.5 Other Configurations with CPWM 247

- 8.5.1 Three-Leg Converter—Two-Phase Machine 247

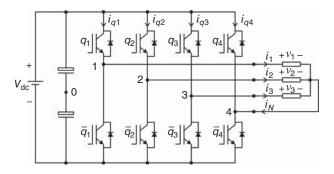

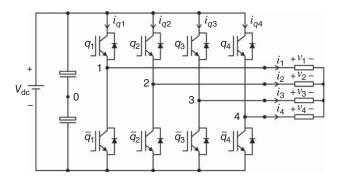

- 8.5.2 Four-Leg Converter 249

- 8.6 Nonconventional Topologies with CPWM 252

- 8.6.1 Inverter with Split-Wound Coupled Inductors 252

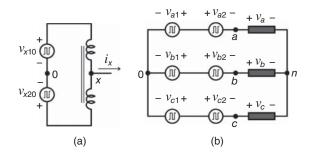

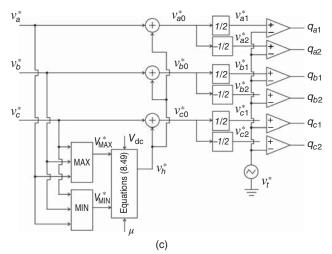

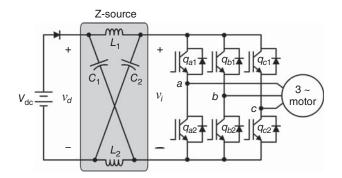

- 8.6.2 Z-Source Converter 254

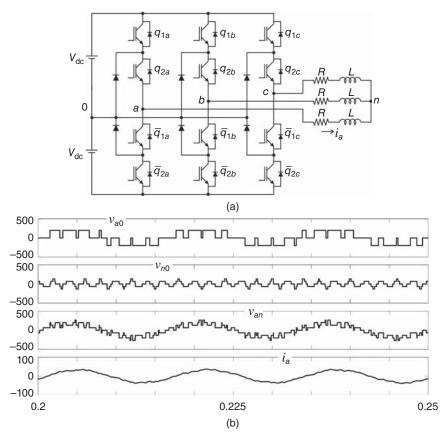

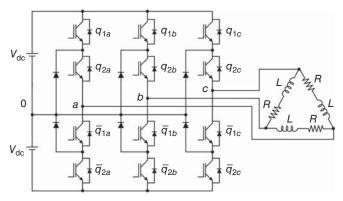

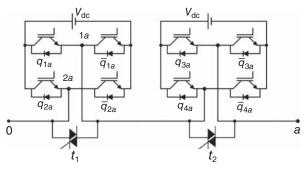

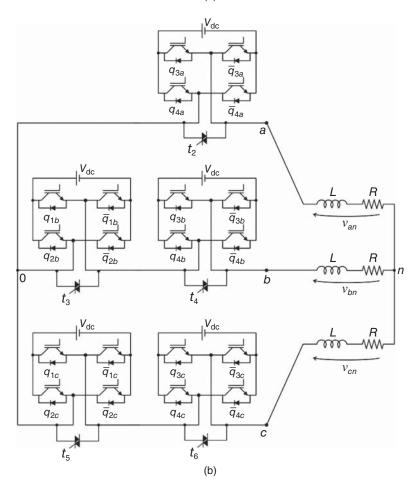

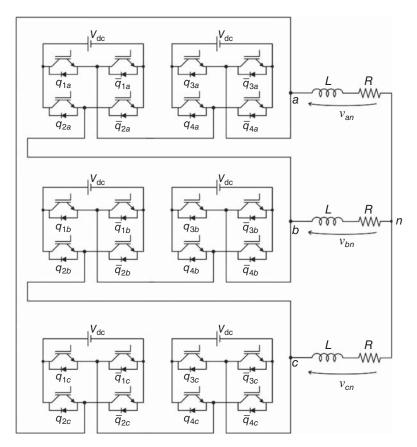

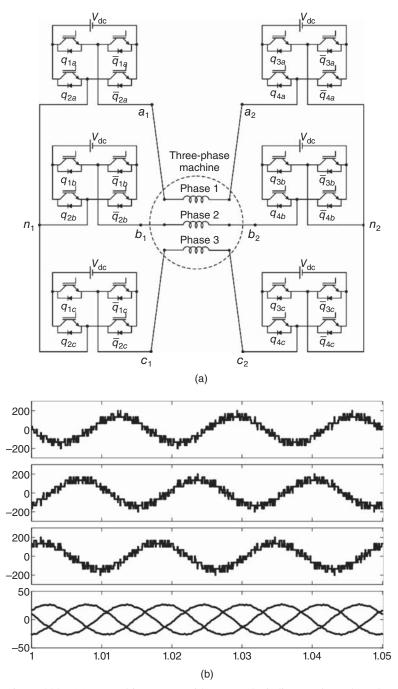

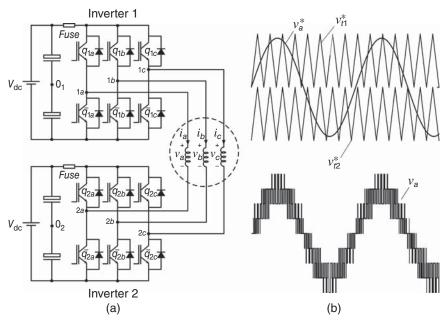

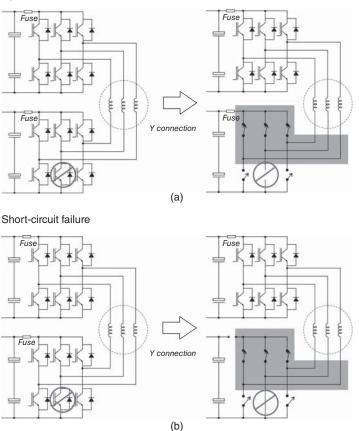

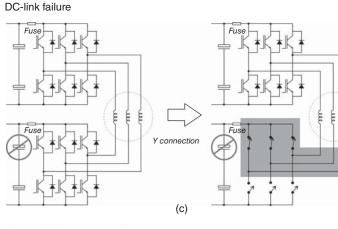

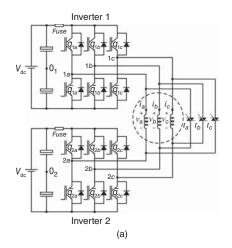

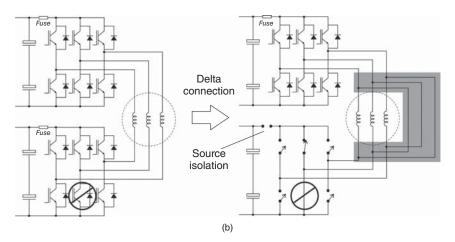

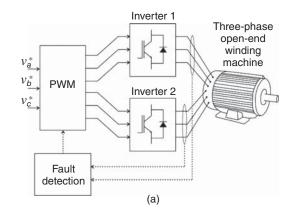

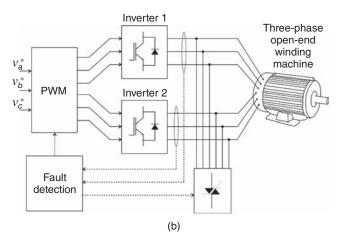

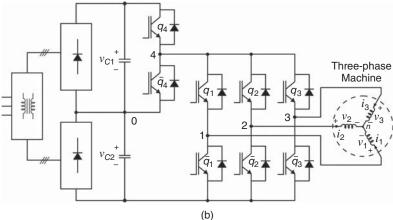

- 8.6.3 Open-End Winding Motor Drive System 257

- 8.7 Summary 261

- References 261

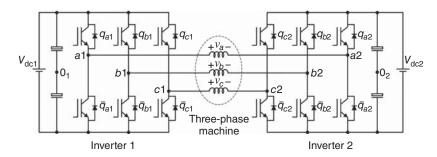

#### CHAPTER 9 CONTROL STRATEGIES FOR POWER CONVERTERS

- 9.1 Introduction 264

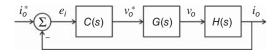

- 9.2 Basic Control Principles 265

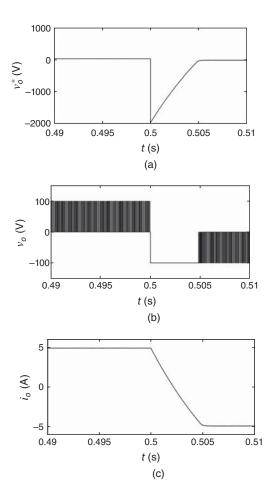

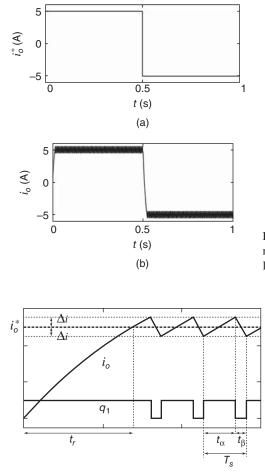

- 9.3 Hysteresis Control 271

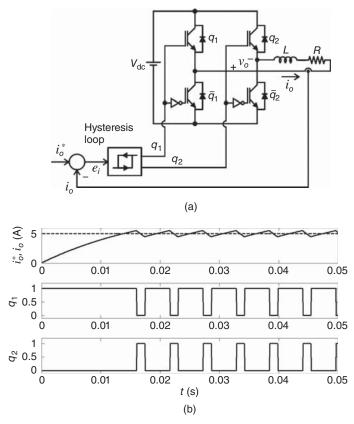

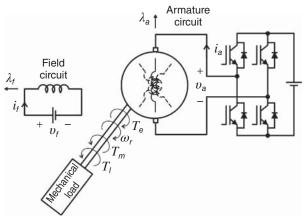

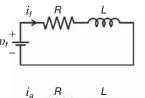

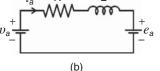

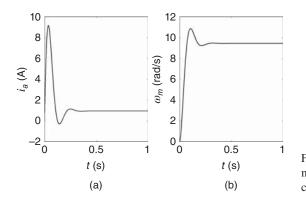

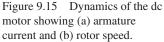

- 9.3.1 Application of the Hysteresis Control for dc Motor Drive 275

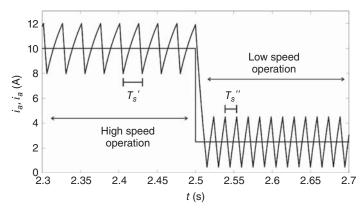

- 9.3.2 Hysteresis Control for Regulating an ac Variable 278

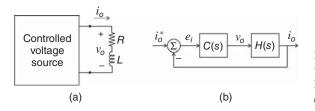

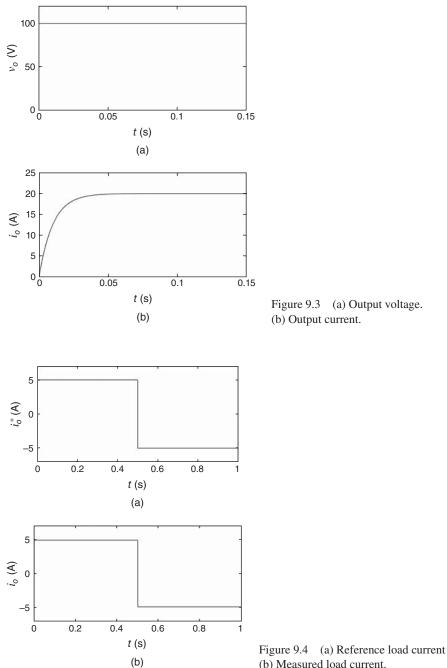

- 9.4 Linear Control—dc Variable 279

- 9.4.1 Proportional Controller: RL Load 279

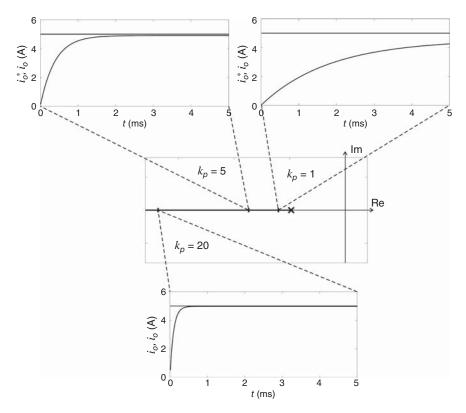

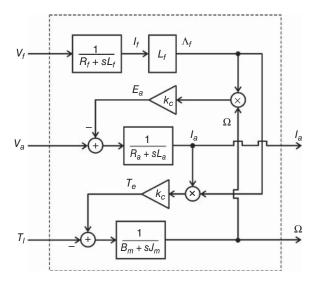

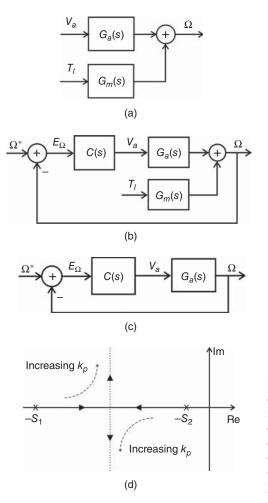

- 9.4.2 Proportional Controller: dc Motor Drive System 280

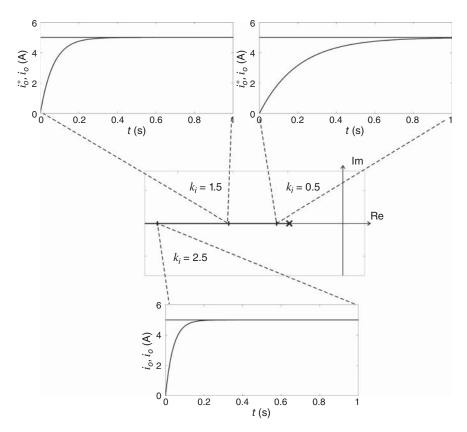

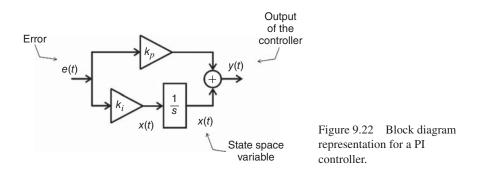

- 9.4.3 Proportional-Integral Controller: RL Load 283

- 9.4.4 Proportional-Integral Controller: dc Motor 285

- 9.4.5 Proportional-Integral-Derivative Controller: dc Motor 286

- 9.5 Linear Control—ac Variable 288

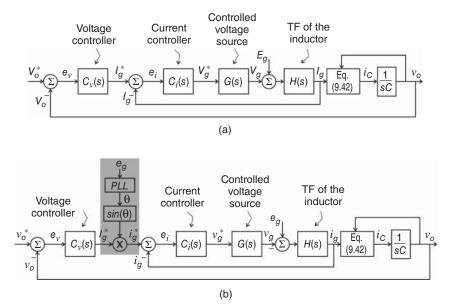

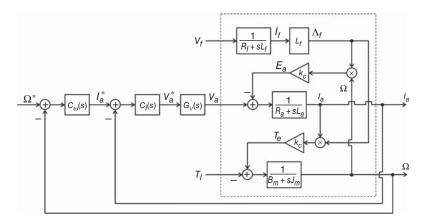

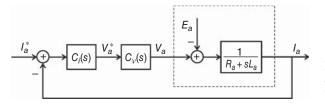

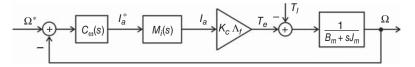

- 9.6 Cascade Control Strategies 289

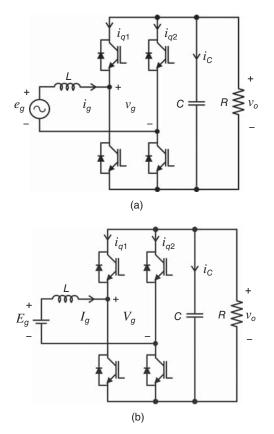

- 9.6.1 Rectifier Circuit: Voltage-Current Control 289

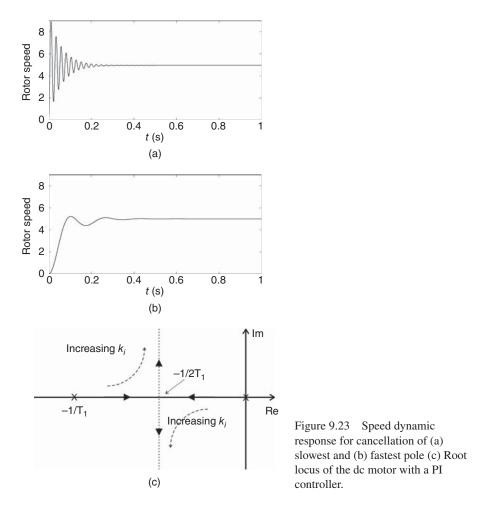

- 9.6.2 Motor Drive: Speed-Current Control 290

- 9.7 Summary 293 References 293

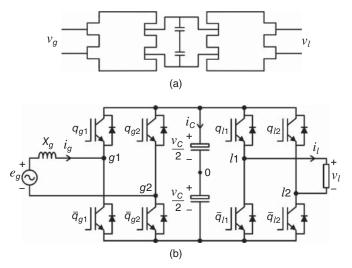

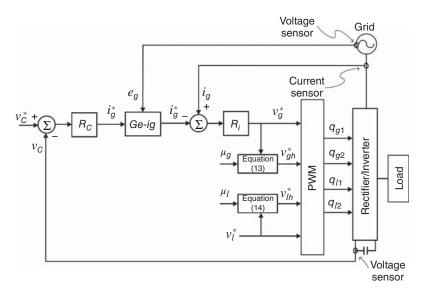

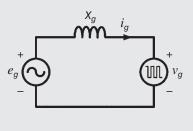

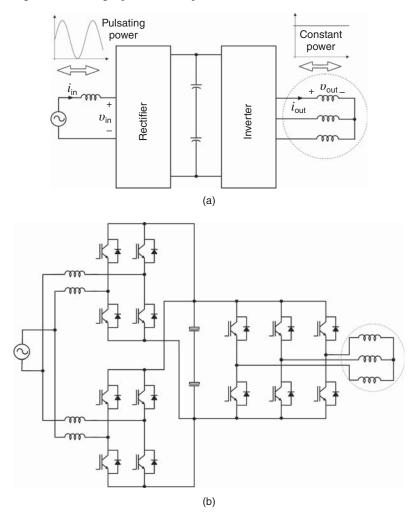

#### CHAPTER 10 SINGLE-PHASE TO SINGLE-PHASE BACK-TO-BACK CONVERTER

| 10.1 | Introduction 295                                                          |

|------|---------------------------------------------------------------------------|

| 10.2 | Full-Bridge Converter 296                                                 |

|      | 10.2.1 Model <b>296</b>                                                   |

|      | 10.2.2 PWM Strategy 297                                                   |

|      | 10.2.3 Control Approach 298                                               |

|      | 10.2.4 Power Analysis 299                                                 |

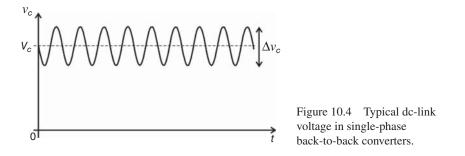

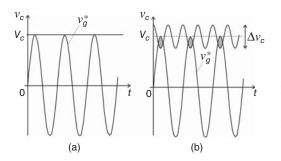

|      | 10.2.5 dc-link Capacitor Voltage <b>301</b>                               |

|      | 10.2.6 Capacitor Bank Design 304                                          |

| 10.3 | Topology with Component Count Reduction 307                               |

|      | 10.3.1 Model <b>307</b>                                                   |

|      | 10.3.2 PWM Strategy <b>308</b>                                            |

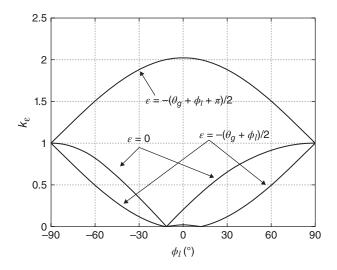

|      | 10.3.3 dc-link Voltage Requirement <b>309</b>                             |

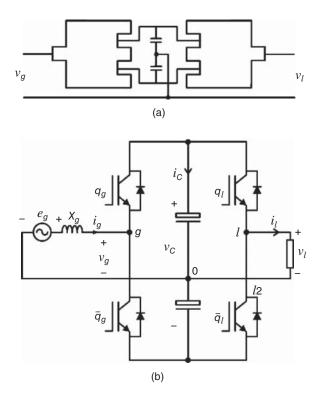

|      | 10.3.4 Half-Bridge Converter <b>310</b>                                   |

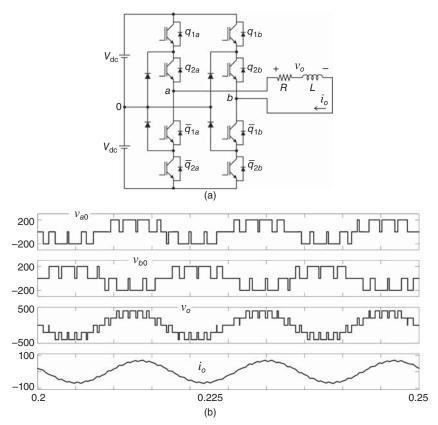

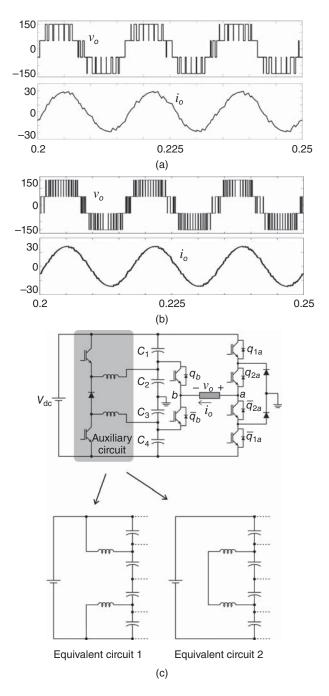

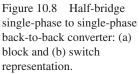

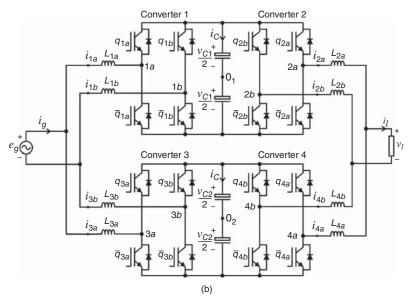

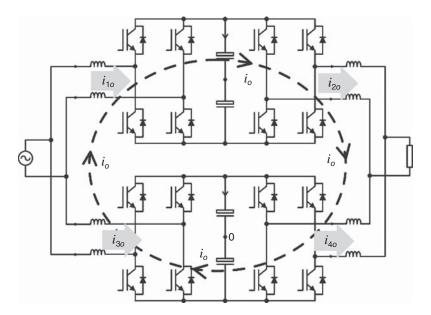

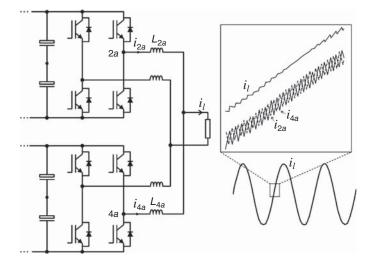

| 10.4 | Topologies with Increased Number of Switches (Converters in Parallel) 310 |

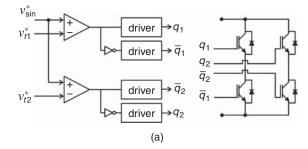

|      | 10.4.1 Model 311                                                          |

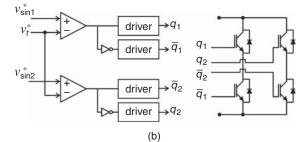

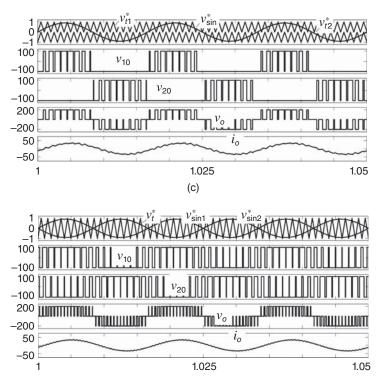

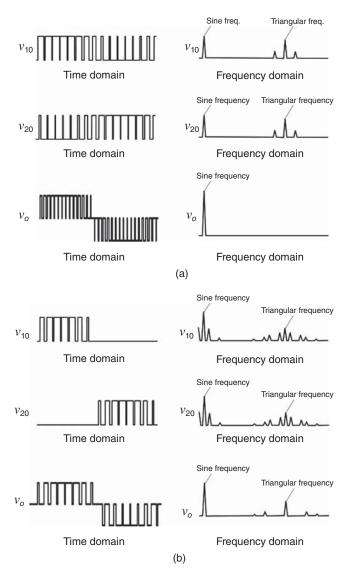

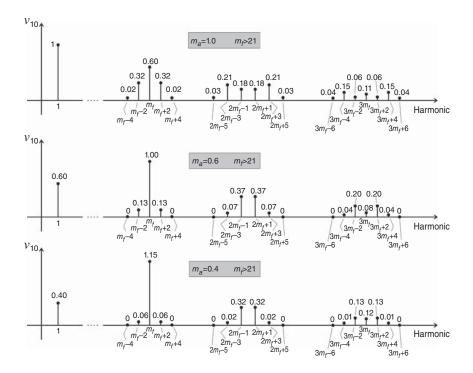

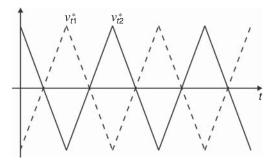

|      | 10.4.2 PWM Strategy <b>315</b>                                            |

|      | 10.4.3 Control Strategy <b>316</b>                                        |

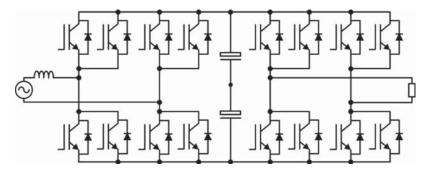

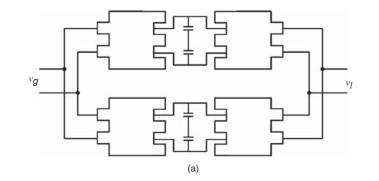

| 10.5 | Topologies with Increased Number of Switches (Converters in Series) 318   |

| 10.6 | Summary 321                                                               |

|      | References 321                                                            |

|      |                                                                           |

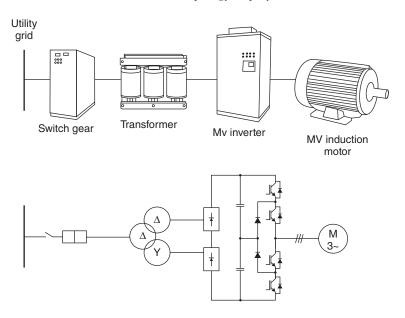

#### CHAPTER 11 THREE-PHASE TO THREE-PHASE AND OTHER BACK-TO-BACK CONVERTERS

324

- 11.1

Introduction

324

11.2

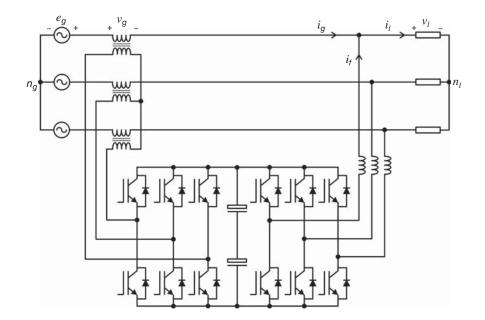

Full-Bridge Converter

325

11.2.1

Model

325

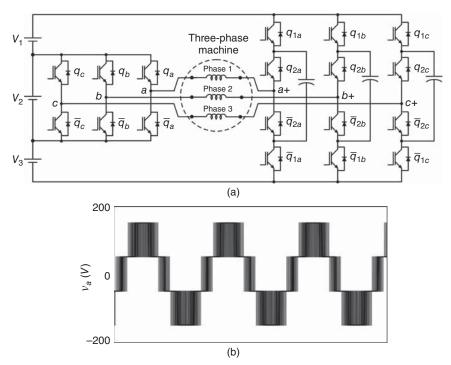

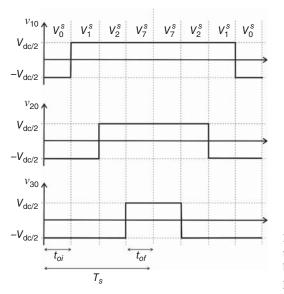

11.2.2

PWM Strategy

327

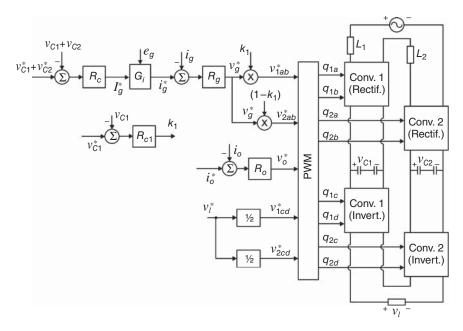

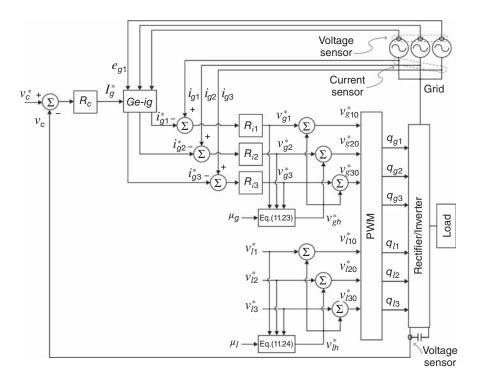

- 11.2.3 Control Approach 328

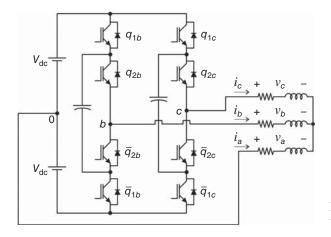

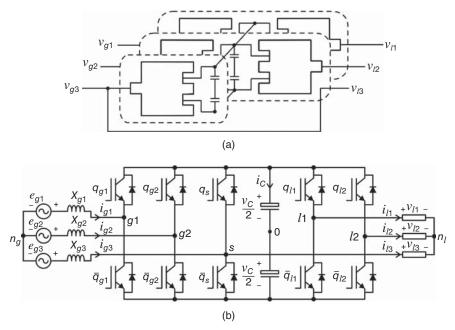

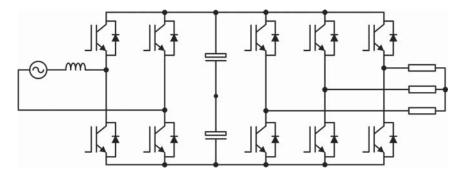

- 11.3 Topology with Component Count Reduction 330

- 11.3.1 Model 330

- 11.3.2 PWM Strategies 331

- 11.3.3 dc-link Voltage Requirement 332

- 11.3.4 Half-Bridge Converter 332

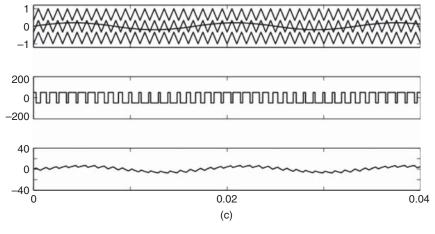

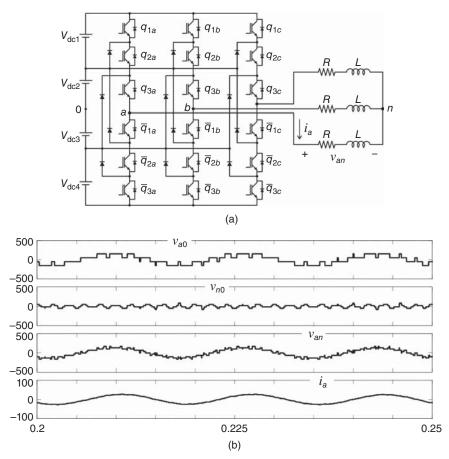

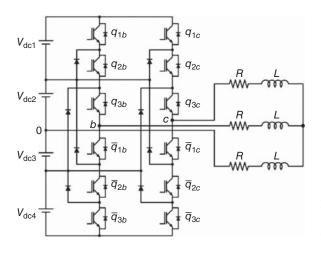

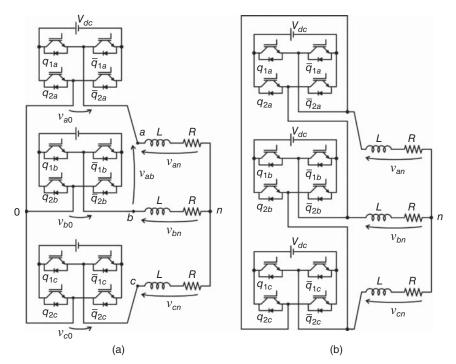

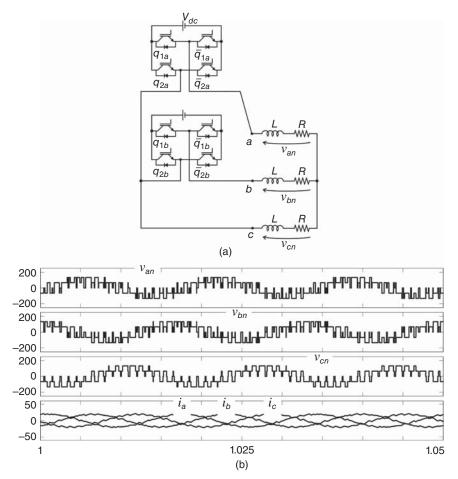

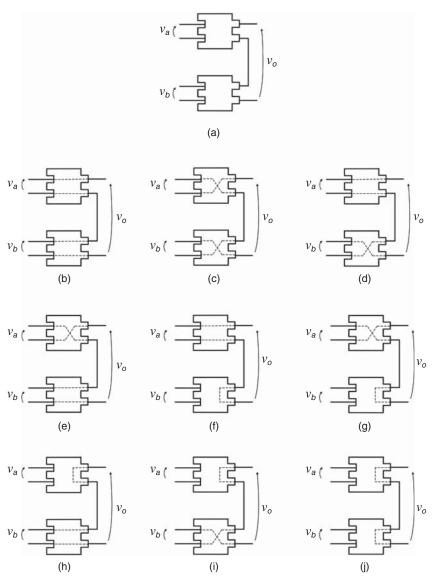

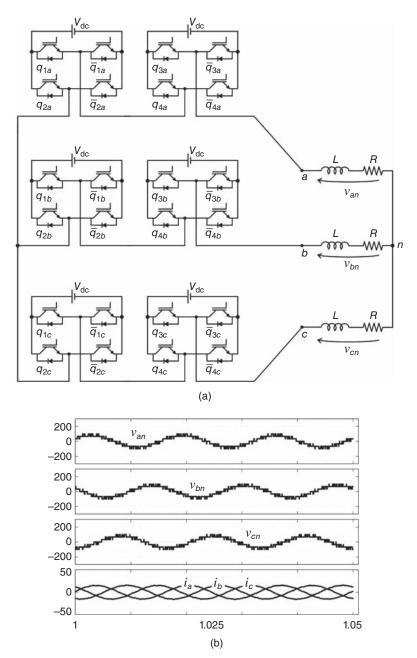

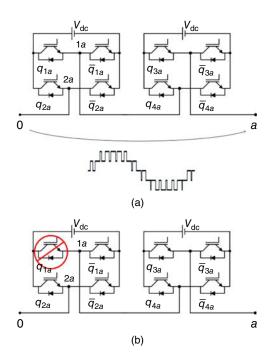

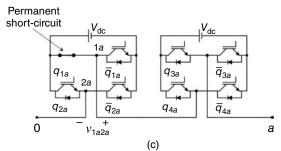

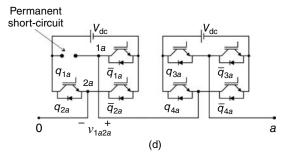

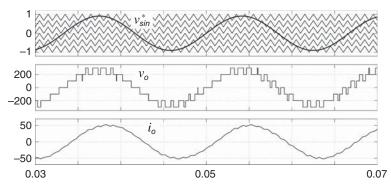

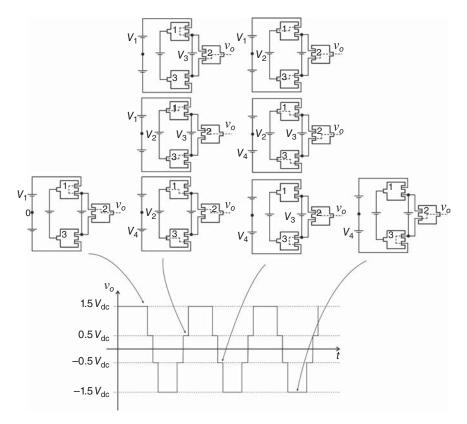

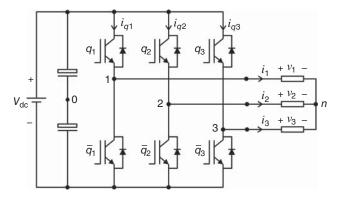

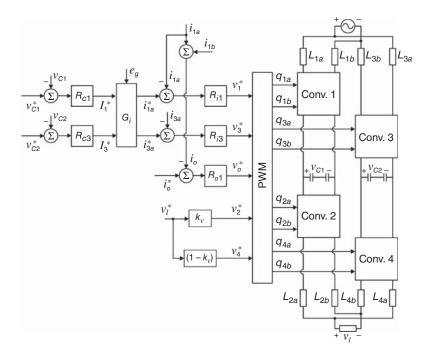

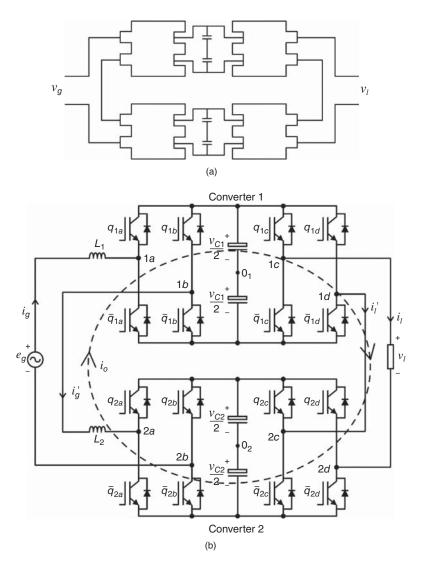

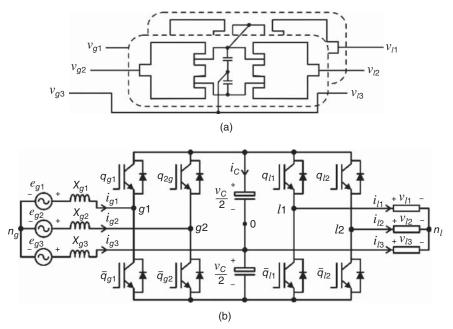

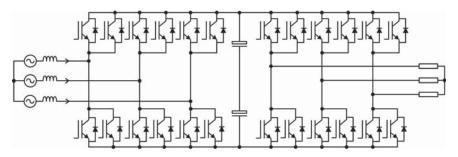

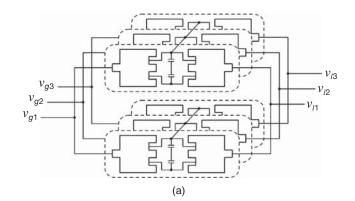

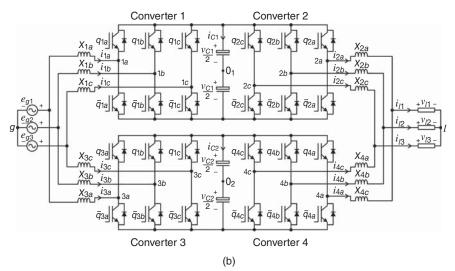

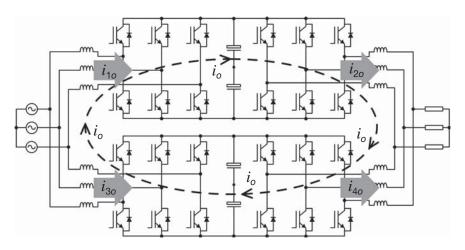

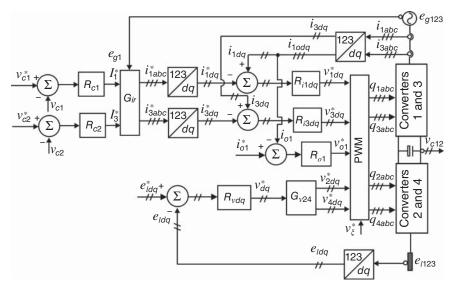

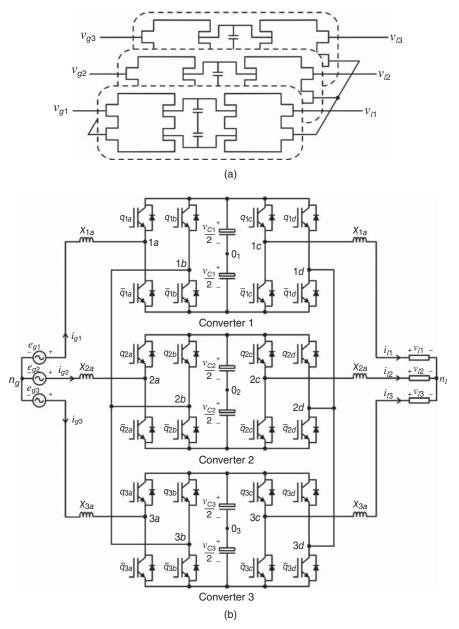

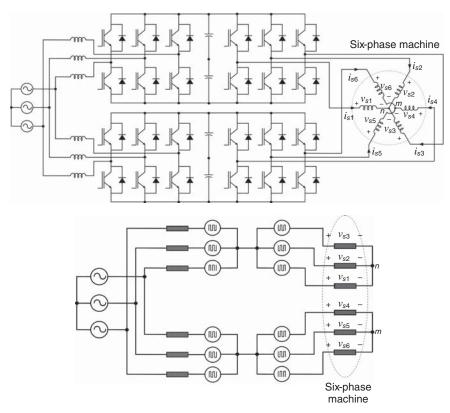

- 11.4 Topologies with Increased Number of Switches (Converters in Parallel) 332 11.4.1 Model 333

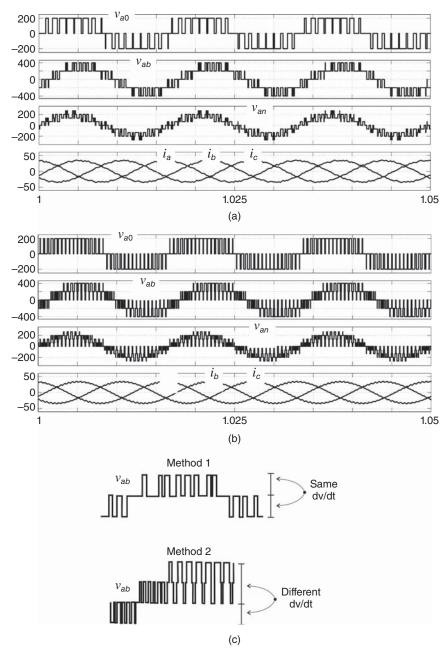

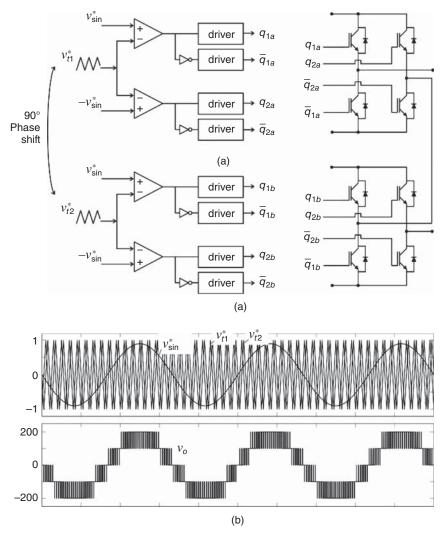

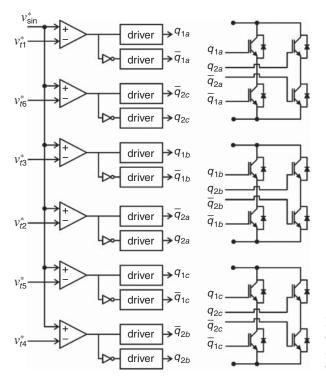

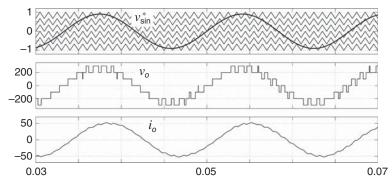

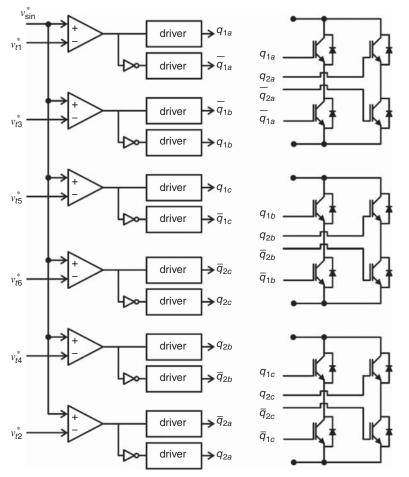

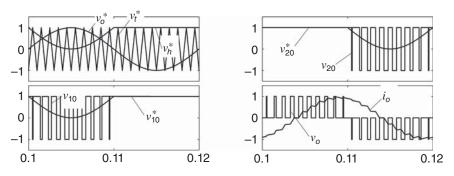

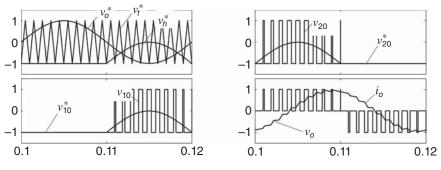

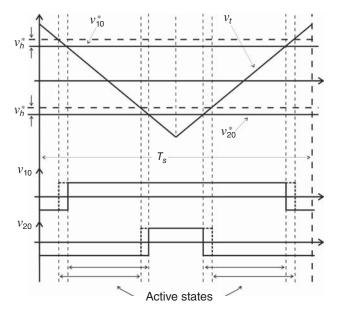

- 11.4.2 PWM 338

- 11.4.3 Control Strategies

- 11.5 Topologies with Increased Number of Switches (Converters in Series) 340

339

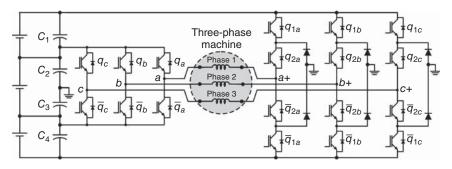

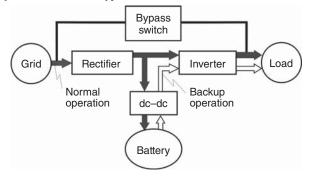

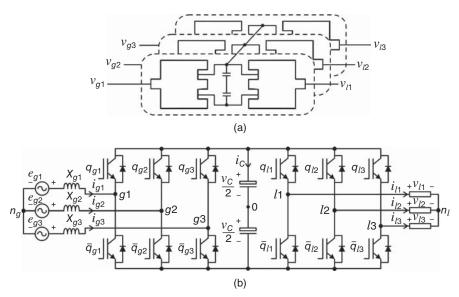

- 11.6 Other Back-To-Back Converters 340

- 11.7 Summary 344 References 344

INDEX

## PREFACE

This book deals with a new methodology to present an important class of electrical devices, that is, power electronics converters. The common approach to teaching converters is to consider each type individually, in a separate and isolated fashion. The direct consequence is that the learning process becomes passive since the power electronics configurations are presented without consideration of their origin and development. Since the teaching process is based on the topology itself, students do not develop the ability to construct new topologies from the conventional ones.

A systematic approach is taken to the presentation of multilevel and back-to-back converters, instead of showing them separately, which is normally done in a conventional presentation. Another special aspect of this book is that it covers only subjects related to the converters themselves. This will give more room for exploring the details of each topology and its concept. In this way, the method of conceptual construction of power electronics converters can be highlighted appropriately.

While presenting the basics of power devices, as well as an overview of the main power converter topologies in Chapter 2, this book focuses primarily on configurations processing ac voltage through a dc-link stage. This text is ideally suited for students who have previously taken an introductory course on power electronics. It serves as a reference book to senior undergraduate and graduate students in electrical engineering courses. However, due to the content in Chapter 2, it is expected that even students who the lack knowledge of power devices and basic concepts of converters can understand the subject.

Although the primary market for this text is heavily academic, electrical engineers working in the field of power electronics, motor drive systems, power systems, and renewable energy systems will also find this book useful.

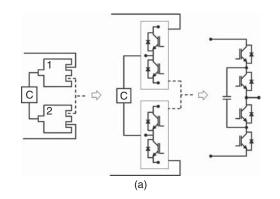

The organization of the book is as follows: Chapter 1 is the introductory chapter. Chapter 2 presents the basics of power devices as well as an overview of the main power converter topologies. Chapter 3 provides a brief review of the main power electronics converters that process ac voltage; additionally, it furnishes the introduction to the power blocks geometry (PBG), which will be used to describe the power converters described in this book. In fact, this chapter brings up a compilation of the topologies explained throughout this book. The fundamentals of PBG and its correlation to the development of power electronics converters are presented in a general way. Multilevel configurations are presented from Chapters 4–7. Neutral-point-clamped, cascade, flying capacitor, and other multilevel configurations are presented in Chapters 4–7, respectively. Chapter 8 deals with techniques for optimization of the pulse width modulation (PWM), considering the fact that the number of pole voltages is higher than the number of voltages demanded by the load. After describing many topologies throughout Chapters 2–7, highlighting the circuits

#### **XII** PREFACE

themselves, as well as PWM strategies in Chapter 8, Chapter 9 handles control actions needed to keep a specific variable of the converter under control. Chapter 9 is strategically placed before the presentation of the back-to-back converters (Chapters 10 and 11) due to their need for regulation of electrical variables. Single-phase to single-phase back-to-back converters are presented in Chapter 10, and the final chapter deals with three-phase to three-phase back-to-back converters.

Euzeli Cipriano Dos Santos Jr. Edison Roberto Cabral Da Silva CHAPTER

## **INTRODUCTION**

## **1.1 INTRODUCTION**

Power electronics may be considered a revolutionary field in electrical engineering because of the new insights obtained during its development. This has actually been the case from the beginning, when mercury arc rectifiers and thyratrons were employed in grid-controlled circuits. After this first generation of power devices and converters, power electronics with silicon power diodes and thyristors was developed to overcome many of the problems of the first generation, such as the operation in low efficiency. As mentioned in Reference 1, the so-called power electronics, with gas tube and glass-bulb electronics, was known as industrial electronics, and the power electronics with silicon-controlled rectifiers began emerging in the market in the early 1960s.

The different definitions of power electronics lead to the same concept or idea: that the control of power flow between an apparatus that furnishes electrical energy and another one that demands electrical energy. For instance, the definition given in References 2 and 3 say, respectively: "... power electronics involves the study of electronic circuits intended to control the flow of electrical energy. These circuits can handle power flow at levels much higher than the individual devices ratings ..." and "... power electronics deal with conversion and control of electrical power with the help of electronic switching devices."

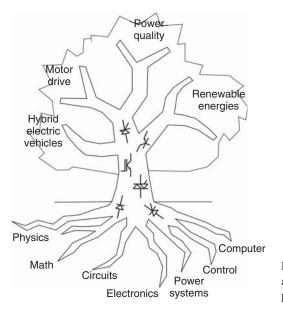

Power electronics involves several academic disciplines creating a complex system, including semiconductor physics, control theory, electronics, power systems, and circuit principles. The comprehensive aspect of power electronics makes the presentation of its contents difficult. The interdisciplinary nature of power electronics requires the integration of the practices and assumptions of all the academic disciplines involved, as well as calling for significant prerequisites on the part of the students enrolled for the course. Figure 1.1 illustrates this by analogy, with the prerequisite skills needed for a power electronics course being shown as the roots of a tree, the various power electronics devices as the trunk, and the resulting technologies and applications (power quality, renewable energy systems, etc.) as the branches.

Since the dawn of solid-state power electronics, the use of semiconductor devices has been the major technology to drive power processors. A comparison

Advanced Power Electronics Converters: PWM Converters Processing AC Voltages,

Forty Fifth Edition. Euzeli Cipriano dos Santos Jr. and Edison Roberto Cabral da Silva.

<sup>© 2015</sup> The Institute of Electrical and Electronics Engineers, Inc. Published 2015 by John Wiley & Sons, Inc.

Figure 1.1 Interdisciplinary nature and new insights obtained from power electronics.

of the semiconductor devices formerly used in controlled rectifiers with new technologies underlines this dramatic development. In addition to the improvement of power switches, there has also been great activity in terms of circuit topology innovations.

A power electronic converter is the centerpiece of many electrical systems. Common applications include, but are not limited to, motor drive systems, renewable energies, robotics, electrical and hybrid vehicles, and circuits promoting power quality. These applications have required considerable research worldwide to develop semiconductor devices, configurations that process ac and dc variables, control and diagnosis, fault-tolerant systems, and the like.

In addition to the technical side mentioned already, the educational aspects have considerable importance, as students usually consider power electronics courses to be particularly difficult, perhaps because of their interdisciplinary nature. Achieving student motivation is thus a fundamental task of educators involved in the field of power electronics.

In this context, this book discusses a novel methodology for presenting an important set of power electronics converters, that is, topologies that process ac voltage. The common approach to teaching converters is to consider each type individually, in a separated and isolated manner. The direct consequence is that the learning process becomes passive as the power electronics configurations are presented without any consideration of their origin and development. Since the teaching process is based on the topology itself, students develop no ability to construct new topologies, different from the conventional ones. Section 1.2 outlines this new methodology.

## 1.2 BACKGROUND

Although presenting the basics of power devices as well as an overview of the main power converter topologies in Chapter 2, this book focuses primarily on configurations processing ac voltage through a dc-link stage. This book is ideally suited for students who have already taken an introductory course in power electronics. It also serves as a reference book to senior undergraduate and graduate students in electrical engineering courses. However, students can easily manage despite the lack of knowledge of power devices and basic concepts of converters, because they are explained in Chapter 2.

Systems with power electronics conversion have been used to guarantee grid and load requirements in terms of controllability and efficiency of the electrical energy demanded, especially in industrial applications. Power electronics topologies convert energy from a primary source to a load (or to another source) requiring any level of processed energy.

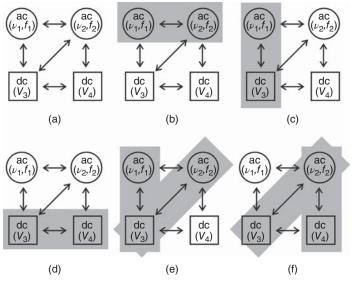

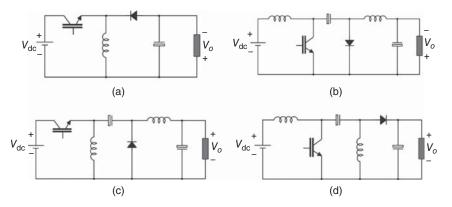

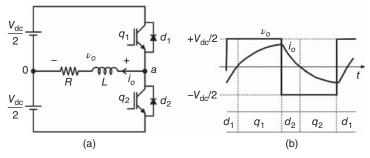

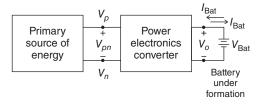

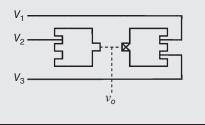

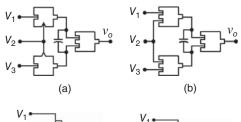

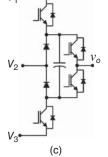

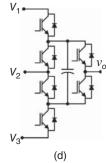

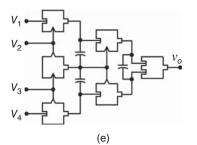

Classifications of the power electronics topologies can be done in terms of the type of variable under control (i.e., ac or dc), as well as the number of stages of power conversions used, as observed in Fig. 1.2. Figure 1.2(a) shows, in a general way, many of the possibilities related to energy conversion. Figure 1.2(b) highlights a direct ac-ac conversion, which converts an ac voltage  $(v_1)$  with a specific frequency  $(f_1)$  to another ac voltage with a different (or same) voltage  $(v_2)$  and frequency  $(f_2)$ ; this converter is normally called a cycle converter. Figure 1.2(c) depicts the ac-dc or dc-ac conversion, while Fig. 1.2(d) shows a dc-dc converter. Even admitting

Figure 1.2 Power conversion: (a) all possibilities of conversion, (b) cycle converter, (c) rectifier or inverter, (d) chopper, (e) ac-dc-ac, and (f) dc-ac-dc.

that Fig. 1.2(e) and 1.2(f) could be considered as extended versions of the previous cases, those conversion systems (ac-dc-ac and dc-ac-dc) are presented in Fig. 1.2 because of the large use in different applications.

Special attention is given to the conversion systems presented in Fig. 1.2(c) and 1.2(e), dealing with configurations that process ac voltage (at input and/or output converter sides) with one dc stage. A systematic approach is taken for the presentation of those configurations, instead of just showing them separately, as is normally done in a conventional presentation. Another aspect of this book is that only the subjects related to the converters themselves will be considered, which means that the contents dealing with either ac filters or transformers will be omitted. This will give more room for exploring the details of each topology and its concept. In this way, the method of conceptual construction of power electronics converters can be highlighted appropriately.

## 1.3 HISTORY OF POWER SWITCHES AND POWER CONVERTERS

Configurations of power electronics converters have provided an attractive alternative for the applications needing energy processing, considering the acceptable level of losses associated with the conversion process itself, as well as improvement in reliability. As previously mentioned, power electronics converters must control the power flow, which means that the development of the devices used in those converters is crucial to guarantee the expected features. In this section, a historic view of the power electronics devices will be furnished, highlighting the main events that contributed to the current development.

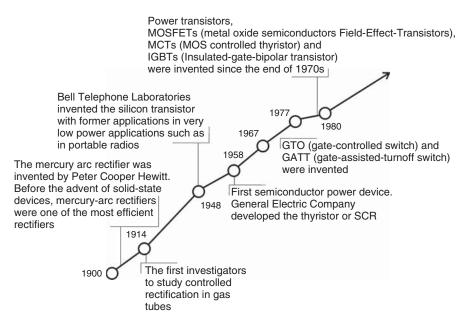

The history of power electronics predates the development of the semiconductor devices employed nowadays. The first converters were conceived in the early 1900s, when the mercury arc rectifiers were introduced. Until the 1950s the devices used to build power electronics converters were grid-controlled vacuum tube rectifier, ignitron, phanotron, and thyratron. There were two important events in the power electronics development: (i) in 1948, when Bell Telephone Laboratories invented the silicon transistor, with applications in very low power devices such as in portable radios and (ii) in 1958, when the General Electric Company developed the thyristors or SCR, first using germaniums and later silicon. It was the first semiconductor power device.

Besides these two events, many developments have been achieved in terms of switching development. Between 1967 and 1977, the gate turnoff (GTO) (gate-controlled switch) and gate-assisted turnoff thyristor (GATT) (gate-assisted turnoff switch) were invented. Power transistors, MOSFETs (metal oxide semi-conductor field-effect-transistors), MCTs (MOS-controlled thyristor) and IGBTs (insulated-gate-bipolar transistors) have been invented since the end of 1970s. In addition, it is worth mentioning that the area of power electronics was deeply influenced by microelectronics development, and the history of power electronics is closely related to advances in integrated circuits to control switching power supplies.

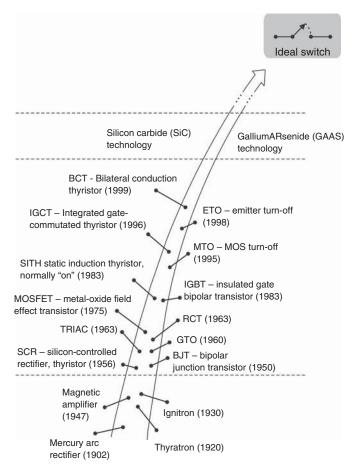

Figure 1.3 Timeline of historical events in the power electronics devices evolution.

Figure 1.3 depicts the timeline showing the development of power electronics devices.

An important chapter in the history of power electronics converters was the development of switching power suppliers. In 1958, the IBM 704 computer, which was developed for large-scale calculations, used as a switching power supplier the primitive vacuum tube-based switching regulator. But the revolution in power supplier concepts came in the late 1960s, when the switching power supplies replaced the linear ones. In a linear power supply, regulated dc voltages are obtained from the ac utility grid throughout the following sequence of steps: (i) 60 Hz power transformer, to converter 120 ac voltage at the primary transformer side to low voltage at secondary transformer side; (ii) such voltage is converted to dc with a simple diode rectifier; and (iii) a linear regulator drops the voltage to a desired value. Indeed, it is possible to identify many problems related to this technology, such as low efficiency (50–65% of the power is wasted as heat), and it was heavy and large (mainly due to the low frequency transformer, heatsink and fans to deal with the heat). The advantages are that it has a very stable output voltage and the conversion system is noise-free.

To overcome the disadvantages of the linear regulators, General Electric published a design of an early stage switching power supply in 1959.

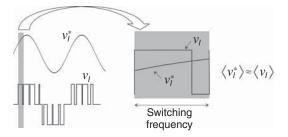

The concept of switching power suppliers is very different from linear regulators. Instead of conducting power 100% of the time (i.e., turning excess power into heat), the switches and passive elements are connected to rapidly turn the power on and off. Unlike linear regulators, the ac utility voltage is converted directly to dc voltage, and the gating signal controls the time of the switching, regulating the average voltage desired at the output converter end. Another important development in power electronics configurations was the controlled rectifiers, especially with the production of the silicon-controlled rectifier (SCR or thyristor). Such a device allowed the control of high power by just changing the signal applied to its gating circuit with higher efficiency rather than the older technology of employing a mercury arc rectifier.

# 1.4 APPLICATIONS OF POWER ELECTRONICS CONVERTERS

The range of applications for power electronics converters is so large that it goes from low power residential applications to high power transmission lines. Many of those applications can be considered as traditional ones (e.g., rectification circuits and motor drive systems). On the other hand, a few emerging applications have generated wide interest (e.g., renewable energy systems). A brief discussion matching the power electronics converters with those applications will be introduced here, with the details of those applications being presented throughout the chapters.

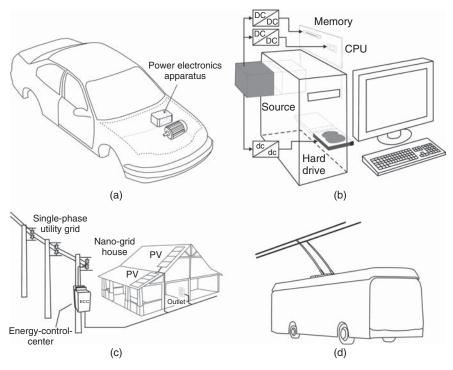

Figures 1.4 and 1.5 summarize some examples that demonstrate the presence of power electronics in a wide range of applications. Figure 1.4(a) shows schematically the application of power electronics in hybrid/electric vehicles. From the power

Figure 1.4 Applications of power electronics using converters that process ac voltage.

Figure 1.5 Application of power electronics in a distributed generation system. C stands for converter.

electronics point of view, the hybrid and fully electric automobiles differ one from another, mainly due to the power ratings of the inverters used. While a typical inverter rating is about 50 kW for the hybrid vehicle, the inverter rating for a fully electric vehicle is about 200 kW. The inverter motor drive system that furnishes energy to the power-train is by far the most important power electronics system used in this kind of application, but the battery charge and other peripheral systems are also crucial. The main features expected in this application are high efficiency performance, compact on-board energy storage, and low manufacturing cost for market competition with conventional thermal-engine vehicles.

Desktop and laptop computers can be considered as systems with on-board distribution schemes where different dc bus voltages are required. Inside these equipment can be found many power electronics converters, as seen in Fig. 1.4(b). An ac-dc converter produces a dc voltage bus from an ac utility grid, which will be employed by different dc-dc converters to supply the microprocessor, disk drive, memory, and so on. In the case of laptops, a battery charger is added with a power management system to control sleep modes, which guarantees extension in battery life via power consumption reduction.

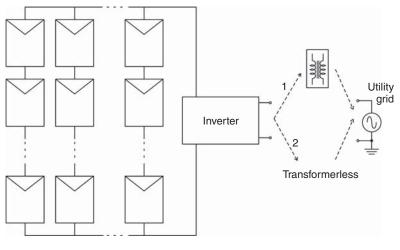

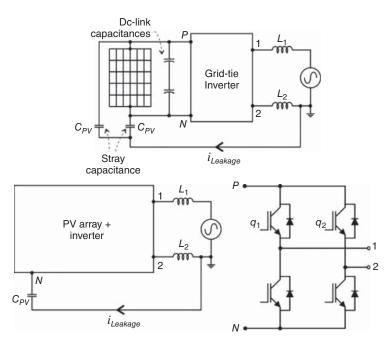

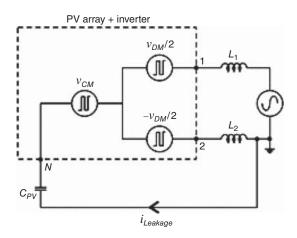

Figure 1.4(c) shows the application of the power electronics converters in renewable energy systems, which nowadays is a hot topic in the political agenda of many industrialized countries, mainly due to environmental issues and as an alternative way to establish a decentralized generation system. It is worth mentioning that, besides the advantages of renewable energy, this kind of system presents a high price energy generation, especially when it is compared to conventional sources such as hydroelectric power and coal. In this sense, power electronics converters must deal with efficiency, reliability, and cost reduction, in order to make those alternative sources of energy more competitive.

Figure 1.4(d) shows a trolley bus, which is an electric bus that receives electrical energy directly from overhead wires (generally suspended from roadside posts) by using spring-loaded trolley poles.

A well-defined traditional power distribution system has a radial topology and unidirectional power flow to feed end-users. However, in the last few years, there has been research and development in replacing this paradigm by a new and complex multisource system with active functions and bidirectional power flow capability. In this new scenario, the utility grid is supposed to guarantee load management and demand side management, as well as using market price of electricity, and forecasting of energy (e.g., based on wind and solar renewable sources) in order to optimize the distribution system as a whole.

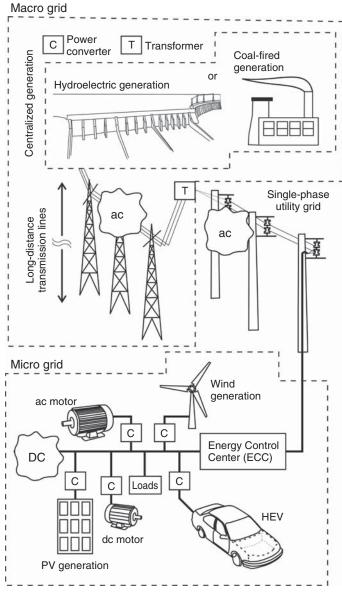

A microgrid can be defined as a localized grouping of electricity generation, energy storage, and loads that are normally connected to a traditional centralized grid (macrogrid), as seen in Fig. 1.5. Figure 1.5 shows a microgrid with a dc bus, where the power converters (represented generically by the letter C) interface distributed sources and loads with the dc bus. The point of common coupling (PCC) between micro- and macrogrid can be disconnected, which means that the microgrid can then operate autonomously. In this case, an island detection system is necessary, which safely disconnects the microgrid. The interface between micro- and macrogrid is possible due to advances made in the power electronics

The important equipment in this scenario is the Energy-Control-Center (ECC), consisting of a bidirectional ac-dc (or dc-ac) power conversion converter used to interface the utility ac grid and dc bus. The multiple dispersed generation sources and the ability to isolate the microgrid from a larger network would provide highly reliable electric power.

Another important area in which power electronics is becoming more and more common is in aerospace industry. Many loads classically powered by hydraulic networks were replaced by electrical power loads (e.g., pumps and braking). Besides facing the common challenges, the power electronics converters must deal with harsh environment constraints in terms of temperature, low pressure, humidity, and vibrations.

## 1.5 SUMMARY

Following the introduction, this chapter presents in Section 1.2 the background of the book, highlighting the type of configurations that this book will deal with (i.e., dc-ac and ac-dc-ac converters). Section 1.3 gives a brief history of the power electronics devices and power electronics converters, focusing on the development of switching power suppliers and SCR rectifiers. Finally, some applications are considered in Section 1.4 to show the wide range of applications of power electronics converters. Readers can find further discussion from References 4 to 13.

## REFERENCES

- Liserre M. Dr. Bimal K. Bose: a reference for generations [editor's column]. IEEE Ind Electron Mag 2009;3(2):2-5.

- [2] Rashid MH. Power Electronics Handbook: Devices, Circuits, and Applications. San Diego, CA: Elsevier; 2007. p 1–2.

- [3] Bose BK. Power Electronics and Motor Drives: Advances and Trends. San Diego, CA: Elsevier; 2006. p 1–3.

- [4] Blaabjerg F, Consoli A, Ferreira JA, van Wyk JD. The future of electronic power processing and conversion. IEEE Trans Ind Appl 2005;41(1):3–8.

- [5] Gutzwiller FW. Thyristors and rectifier diodes the semiconductor workhorses. IEEE Spectr 1967;4:102–111.

- [6] Elasser A, Kheraluwala MH, Ghezzo M, Steigerwald RL, Evers NA, Kretchmer J, Chow TP. A comparative evaluation of new silicon carbide diodes and state-of-the-art silicon diodes for power electronic applications. IEEE Trans Ind Appl 2003;39(4):915–921.

- [7] dos Santos EC Jr, Jacobina CB, da Silva ERC, Rocha N. Single-phase to three-phase power converters: state of the art. IEEE Trans Power Electron 2012;27(5):2437–2452.

- [8] Goldman A. Magnetic Components for Power Electronics. Kluwer Academic Publishers; 2002.

- [9] IBM Customer Engineering Reference Manual: 736 Power Supply, 741 Power Supply, 746 Power Distribution Unit; 1958. p 60–17.

- [10] Karcher EA. Silicon controlled rectifiers in monolithic integrated circuits. Electron Devices Meeting, 1965 International; vol. 11; 1965. p 6–17.

- [11] Mohan N, Undeland TM, Robbins WP. Power Electronics: Converters, Applications, and Design. 3rd ed. John Wiley & Sons; 2002.

- [12] Rashid MH. Power Electronics: Circuits, Devices, and Applications. Prentice Hall; 1993.

- [13] El-Hawary ME. Principles of Electric Machines with Power Electronic. Wiley: IEEE Press; 2002.

# POWER SWITCHES AND OVERVIEW OF BASIC POWER CONVERTERS

## 2.1 INTRODUCTION

The basic principles and characteristics of the main power switches are presented in this chapter. Furthermore, an overview of the principal power electronics converters is furnished, highlighting the main characteristics for each type of topology. Semiconductor power devices are the center piece of the power electronics converters. While the knowledge about such devices is crucial to design a power converter with specific characteristics for a given application, the study of different topologies brings up new possibilities to improve the energy process system.

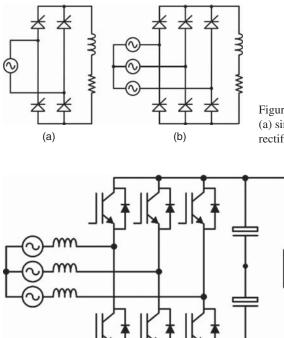

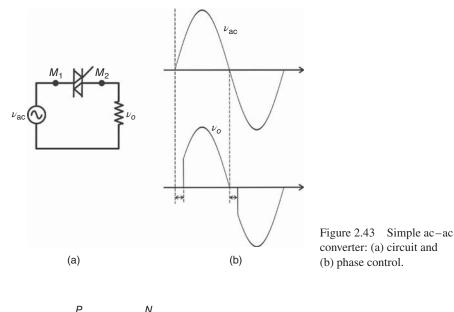

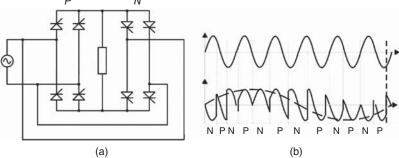

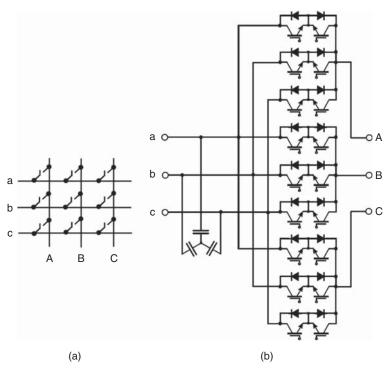

Before dealing specifically with pulse-width modulation (PWM) converters processing ac voltage, which is the core of this book, this chapter considers a large variety of power conversion possibilities. The converters studied in this chapter include dc-dc, dc-ac, ac-dc, and ac-ac converters, as well as voltage-, and current-source converters.

As the objective is to furnish an overview of the different types of switches and converters, a deep analysis of the converters described in this chapter is omitted. However, the following chapters present a systematic description of both power converters, called Power Block Geometry, and the advanced PWM converters processing ac voltage (e.g., multilevel converters and back-to-back converters) to the smallest detail.

This chapter is organized as follows: Section 2.2 presents the ideal characteristics of the major power switches available in the market, highlighting their static and dynamic features; Section 2.3 shows the real characteristics of such semiconductor devices, sorted in terms of dynamic characteristics; Section 2.4 describes basic power electronics converters, and finally, Section 2.5 summarizes the chapter.

Advanced Power Electronics Converters: PWM Converters Processing AC Voltages,

Forty Fifth Edition. Euzeli Cipriano dos Santos Jr. and Edison Roberto Cabral da Silva.

$<sup>@\ 2015\</sup> The\ Institute\ of\ Electrical\ and\ Electronics\ Engineers,\ Inc.\ Published\ 2015\ by\ John\ Wiley\ \&\ Sons,\ Inc.\ Published\ 2015\ by\ John\ Wiley\ \&\ Sons,\ Inc.\ Published\ 2015\ by\ John\ Wiley\ Barrow\ Sons,\ Inc.\ Published\ 2015\ by\ John\ Wiley\ Barrow\ Sons,\ Inc.\ Published\ 2015\ by\ John\ Wiley\ Barrow\ Sons,\ Inc.\ Sons\ Son$

# 2.2 POWER ELECTRONICS DEVICES AS IDEAL SWITCHES

The design and construction of power semiconductor devices focus on how to improve their performance toward the hypothetical concept of an ideal switch. Figure 2.1 shows the power switches and the year of development of each switch. The performance of a given power switch is normally measured by its static and dynamic characteristics. An ideal switch must have the following characteristics: (i) infinite blocking voltage capability, (ii) no current while the switch is off, (iii) infinite current capability when on, (iv) drop voltage equal to zero while on, (v) no switching or conduction losses, and (vi) capability to operate at any switching frequency.

There are different ways to classify a power switch. In this book, two different ways are considered: static characteristics and dynamic controllability. The main

Figure 2.1 Development of the power switches toward the concept of the ideal switch.

figures of merit for the static characteristics are the graphs describing the current versus voltage behaviors (I-V). On the other hand, for the dynamic features, the capability to change the states on and off through either an external signal (gating command) or by the variables of the circuit in which the switch is connected is considered. For example, there is no gating signal to turn on and off a diode, its conduction or blocking depends upon the voltage and current imposed by the circuit.

#### 2.2.1 Static Characteristics

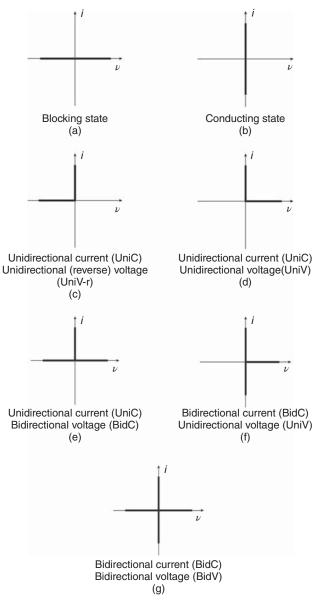

The static characteristics of the power semiconductor devices are related to their ability to either conduct or block one or two polarities, as shown in Fig. 2.2.

Figure 2.2(a) and 2.2(b) shows the ideal I-V characteristic for the blocking and conducting states, respectively. Figure 2.2(c)-2.2(g) depicts the voltage versus current (I-V) ideal characteristics for the main devices found in the market.

The semiconductor devices can, therefore, operate with either unidirectional or bidirectional (UniC or BidC) current, and with either unidirectional or bidirectional voltage (UniV or BidV). For example: (i) diode, bipolar junction transistor (BJT), and insulated bipolar junction transistor (IGBT) are unidirectional voltage and current type of devices, (ii) SCR is an unidirectional current and bidirectional voltage device, (iii) TRIAC and bidirectional controlled thyristor (BCT) are bidirectional in current and voltage, and (iv) MOSFET is unidirectional in voltage and bidirectional in current.

The characteristics presented in Fig. 2.2(c)-2.2(g) play an important role for the specification and design of the power electronics converters. These graphs are in fact approximations of the real I-V characteristics of the device. For example, Fig. 2.2(c) is an approximation of the real characteristics of a power diode, which is presented later in this chapter.

### 2.2.2 Dynamic Characteristics

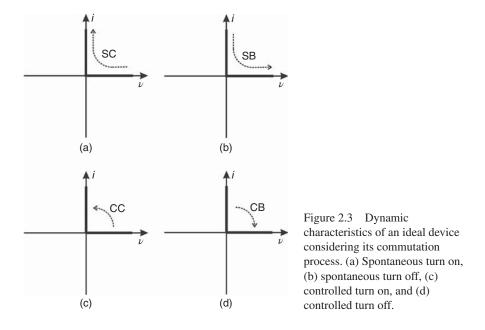

The dynamic characteristics of a specific device are related to the behavior of voltage and current when there is a change either from conduction to blocking state or from blocking to conduction. Such a change is known as commutation or switching. The commutation (or switching) from the blocking state to the conduction state is referred to as either turn-on or conduction. The commutation from the conduction state to the blocking state is referred to as either turn-off or blocking. For the I-V characteristic curves (shown in Fig. 2.2), the commutation process corresponds to going from the operating point on an axis to another one. For example, for a switch UniC/UniV with direct voltage as in Fig. 2.2(c), the blocking procedure makes the variables of the switch (voltage and current) go from the I-axis to the V-axis.

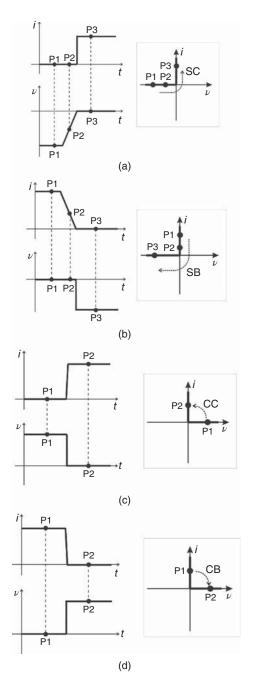

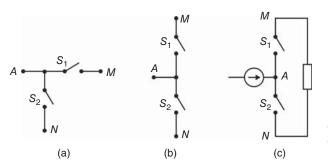

In fact, the commutation process can be spontaneous or controlled, as shown in Fig. 2.3. Four cases are presented as follows:

- Spontaneous conduction (SC)—see Fig. 2.3(a);

- Spontaneous blocking (SB)—see Fig. 2.3(b);

Figure 2.2 Ideal I-V characteristics for blocking and conduction states of the power switches available in the market.

- Controlled conduction (CC)—see Fig. 2.3(c);

- CB—see Fig. 2.3(d).

In the case of spontaneous commutation (i.e., conduction and blocking), the change of state is defined by the variables of the power circuit, while for the controlled

commutation, the change of state is guaranteed via a gating signal (command signal).

Figure 2.4 shows the behavior of the voltage and current in time-domain (left side) and dynamic characteristics (right side) for SC, SB, CC, and CB. The points (P1, P2, and P3) along with the axes in Fig. 2.4 illustrate the behavior of the variables when the switching process occurs for both spontaneous and controlled commutation. For example, in Fig. 2.4(a) P1 indicates the operation point when the switch is blocked, which means that such a device is submitted to a negative voltage while its current is zero. The operation point P2 shows the device's behavior while its voltage has been reduced. Finally, P3 shows the values of voltage and current when the switch is turned on. This commutation process occurs, for example, in a rectifier circuit with diodes where the circuit itself allows the state change from blocking to conduction. A similar analysis can be done for SB in Fig. 2.4(b).

On the other hand, a controlled commutation device must have a control electrode, usually called a gate or base, in addition to the two main terminals. A control signal applied to the gate or base, while the voltage applied between the main terminals is positive, results in change of state in a desirable manner, that is, from one axis to another, as shown in Fig. 2.4(c) and 2.4(d).

In terms of dynamic characteristics, the ideal power devices can be classified as follows:

- SC/SB;

- CC/SB;

- CC/CB;

- SC/CB.

Figure 2.4 Comparison on time-domain and dynamic characteristics during the commutation process. (a) SC, (b) SB, (c) CC, and (d) CB.

## 2.3 MAIN REAL POWER SEMICONDUCTOR DEVICES

The most common power electronics devices are diodes, thyristors, and power transistors. Usually they have two power terminals (anode/cathode, or collector/emitter or drain/source) and one or more command terminals (gate/ base). Unlike the ideal characteristics presented earlier, real devices have practical limits for rated voltage and current, as well as for their operation frequency. Such limits are normally specified by the datasheet furnished by manufacturers. Therefore, the device characteristics and their specification are crucial to choose a particular power device instead of others.

The most common nonideal device characteristics are

- (a) *The Forward and Reverse Voltage Capability*. The main limiting ratings are as follows:

- i. *Forward Blocking Voltage*. The maximum repetitive forward voltage that can be applied to the power terminals of the device (normally from anode to cathode, from collector to emitter, from drain to source) so that the device blocks the current flow (blocking state) in the direct sense, unless commanded to turn on.

- ii. *Reverse Blocking Voltage*. The maximum repetitive reverse voltage that can be applied to the power terminals of the device (from cathode to anode, for instance) so that the device blocks the current flow in the reverse sense.

- iii. *Maximum Peak Nonrepetitive Forward and Reverse Voltage*. The maximum nonrepetitive forward and reverse voltages, respectively, under transient conditions.

- iv.  $V_{dc}$  and  $V_R$ . Maximum continuous direct (forward) and reverse blocking voltages, respectively. This is the maximum dc voltage that the diode can withstand in reverse-bias mode on a continual basis.

- v. *Forward Voltage Drop*. This is the instantaneous value of the drop voltage, which is normally dependent on the temperature.

- (b) The current capability while the device is on (conducting) is junction temperature-dependent. The main limiting ratings are the following:

- i. On-State Current. It is the average value of the conduction current.

- ii. *On-State Root Mean Square (RMS) Current.* It is the RMS value of the conduction current.

- iii. *Peak Repetitive Forward Current*. It is the maximum repetitive current that can flow through the device.

- iv. *Peak Surge Forward Current*. It is the maximum nonrepetitive forward current that can flow through the device under transient conditions.

It should be noted that when blocked, the device still conducts a leakage current that can be forward or reverse, depending on the device state.

- (c) The switching is not instantaneous, so there are limits in the switching frequency, as follows:

- i. Turn-On Time. It is the time required to complete the turn-on process.

- ii. *Turn-Off Time or Recovery Time*  $(t_{rr})$ . it is the minimum interval of time required from the instant the conduction current is decreased to zero so that the device is capable of withstanding the forward voltage without turning on.

- iii. dv/dt. It is the maximum variation rate of the forward voltage that can be applied to the device in the blocking state without starting a nonprogrammed turn-on.

- iv. di/dt. It is the maximum variation rate of the forward current during turn-on that can be applied to the device; higher di/dt than the one specified by the manufacturer may destroy the component.

- (d) The maximum switching frequency depends on the recovery time of the device.

- (e) Power Losses. There are three main components of losses in a semiconductor device: (i) switching losses (turn-on and turn-off), (ii) conduction losses, and (iii) reverse conduction losses.

The most used devices in industrial applications are considered in the following section. Such switches are sorted in terms of their dynamic characteristics.

## 2.3.1 Spontaneous Conduction/Spontaneous Blocking

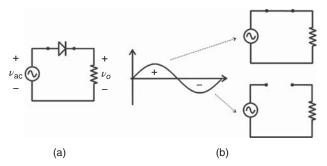

The conventional diode and the Schottky diode have the characteristic of SC and SB, as presented in the sequence.

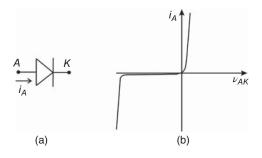

**The Conventional Diode** The conventional diode is a silicon p-n junction device with two terminals, anode (*A*) and cathode (*K*), that conducts current from *A* to *K* and blocks the reverse current. The rating of the voltage goes up to 9 kV with 4.8 kA and 5 kV with 13 kA. Its symbol is presented in Fig. 2.5(a) and its real I-V characteristic is given in Fig. 2.5(b). The diode conducts when  $v_{AK} > 0$ , the current being limited by the external circuit, its typical direct voltage drop is 0.7 V. Generally speaking, it can be said that they recover their reverse blocking capability when the forward current  $i_A$  goes to zero and a reverse voltage is applied across its terminals, for an interval of time longer than the reverse recovery time  $t_{rr}$  obtained in its technical data sheet. In reality, after reaching zero, the current reverses its direction, reaching a reverse peak called "peak reverse recovery current" that is comparable to the forward current. Snubber

Figure 2.5 The diode: (a) symbol and (b) I-V characteristic.

circuits are essential for the adequate protection of the diode. The snubber circuit will protect it from overvoltage spikes, mainly due to the junction capacitance and leakage inductance from terminals and circuit connections. The basic snubber circuit is composed of a capacitor in series with a resistor connected in parallel with the diode. The size of the snubber circuit is reduced for the fast ( $t_{\rm rr} < 1 \,\mu$ s) and ultrafast recovery diode ( $t_{\rm rr} < 100 \,\mathrm{ns}$ ), with ratings reaching: (i) 600 V, 30 A and  $t_{\rm rr} = 50 \,\mathrm{ns}$ , and (ii) 1200 V, 120 A,  $t_{\rm rr} = 85 \,\mathrm{ns}$ . Recent development in the silicon carbide material allows reducing the diode reverse recovery time up to 16 ns.

**The Schottky Diode** Unlike the standard diode presented previously, the Schottky diode is formed by a metal-semiconductor junction (the *p* material is replaced by metal). It has a lower conduction drop voltage (typically 0.5 V) and faster switching time than the standard diode (less than 100 ps), which allows its operation in higher frequency. However, it has lower blocking voltage (typically up to 200 V) and higher leakage current. Its silicon carbide (SiC) version is promising and has been already tested to withstand 1.2 kV with 60 A.

## 2.3.2 Controlled Conduction/Spontaneous Blocking Devices

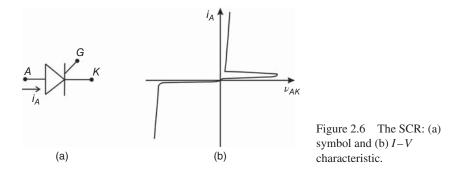

The main devices in this group are the silicon-controlled rectifier (SCR) and the TRIode AC (TRIAC).

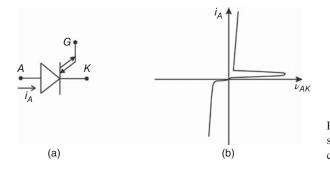

**The SCR** The SCR is a silicon p-n-p-n device with three terminals: two power terminals, anode (A) and cathode (K) through which the current flows, and a control terminal, named the gate terminal (G). It is unidirectional in current and blocks in both forward and reverse directions (UniC/BidV). The device is triggered by a positive gate current pulse. When the gate is not triggered the SCR blocks the current in the forward direction even with  $v_{AK} > 0$ . If  $i_{GK} > 0$  while  $v_{AK} > 0$ , the SCR conducts the current from anode to cathode imposed by the circuit in which the SCR is inserted. Its voltage drop in conduction is from 1 to 4 V. Once in conduction, the SCR behaves like a diode and it can only be turned off when the anode current becomes zero. After the current reaches zero, a reverse voltage should be applied across its terminals in order to accelerate the capability of forward blocking. Note that the gate loses control over the SCR during its conduction. The symbol and real I-V characteristics are shown in Fig. 2.6(a) and 2.6(b), respectively. The direct and reverse voltages across its terminals are symmetrical in the conventional SCR (there are SCRs with asymmetrical voltage characteristics, the ASCR) and can reach 5 kV with 5 kA and 12 kV with 2.3 kA, or even 5 kV with 8 kA. Unexpected turn-on can occur due to a high dv/dt. For these reasons a snubber circuit with a capacitor can be used to avoid both triggering by dv/dt and overvoltage spikes, a resistor that limits the current peak, and an inductor that limits the di/dt rate.

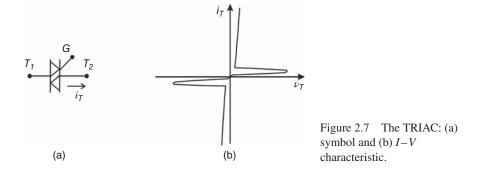

**The TRIAC** The TRIAC is a thyristor that operates as two SCRs monolithically integrated connected in antiparallel. Such a device can conduct and block in both forward and reverse directions (BidC/BidV). It has two power terminals,  $T_1$  and  $T_2$ , and one gate G. Its symbol and its I-V characteristic are presented in Fig. 2.7(a) and

2.7(b), respectively. When  $v_T = v_{T1} - v_{T2}$  is positive (quadrant I) and the TRIAC is turned on by a positive gate current pulse. But when the  $v_T$  is negative (quadrant III) it is turned on by a negative gate current pulse. The operation in quadrants II and IV is also possible but the gate triggering is less sensitive in these cases. Also, the dv/dt is poorer than that of SCRs.

Other CC/SB devices are the light-activated SCR (LASCR), the reverse conducting thyristor (RCT), which functions as an SCR with an inverse-parallel diode (BidC/UniV), and the BCT, in which two SCRs are also connected in antiparallel, but differently from the TRIAC, each one acting independently with its independent gate control (BidC/BidV).

### 2.3.3 Controlled Conduction/Controlled Blocking Devices

The main CC and CB devices are (1) basic transistors, like the BJT and the metal oxide semiconductor field-effect transistor (MOSFET); (2) basic thyristors, like the gate turn-off (GTO); (3) mixed transistors, like the IGBT; and (4) mixed thyristors, like the MOS-controlled thyristor (MCT) and the Integrated gate commutation thyristor (IGCT).

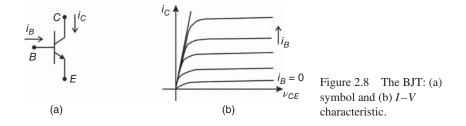

**Bipolar Junction Transistor (BJT)** Unidirectional in current, the BJT can be either n-p-n or p-n-p and it has asymmetric blocking, only withstanding some tens of reverse blocking voltage (UniC/UniV). Its symbol and static characteristics

are shown in Fig. 2.8. It has three terminals, the collector (*C*) and emitter (*E*) through which the current ( $i_c$ ) flows and the base (*B*) that controls the amplitude of  $i_c$ . Unlike lower power BJT devices, the power devices operate in the quasi-saturated region, which reduces the stored charge, avoiding the long recovery time obtained when operated in the saturated region. As its dc current gain ( $h_{fe}$ ) is much lower than its signal level counterpart (in general as low as 5), the Darlington connection is more common because its dc current gain is higher. A disadvantage of this arrangement is its drop voltage and leakage current. BJTs with forward blocking voltage up to 1 kV are available.

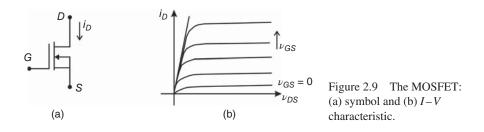

**The MOSFET** Application of the metal oxide semiconductor (MOS) technology to the field-effect transistor resulted in the power MOSFET. It has three terminals, the drain (D), the source (S), and the gate (G).

Its symbol and I-V characteristics are shown in Fig. 2.9. It is an n-p-n, or p-n-p, device in which its two p-n, or n-p, layers are connected through a metal, so that a capacitor is formed between G and D. The MOSFET is turned on by a voltage pulse. The MOSFET acts as a resistance while conducting and behaves like a transistor before being turned on. Similar devices have been developed under different names, depending on the manufacturer, such as the HEXFET ("hexagonal-field-effect-transistor"), SIPMOS ("Siemens-Power Metal Oxide Silicon") and TMOS ("T flowing current metal oxide silicon"). Its forward blocking voltage is in the range of 1 kV and it can operate in high frequency. Since it has an intrinsic diode in antiparallel connection, it operates with forward and reverse current and can be classified as a BidC/UniV device. It has replaced the BJT in the range of low voltage and high frequency but its disadvantage comes from its high conduction resistance that increases with the voltage.

However, it has been demonstrated that SiC MOSFET can have extremely low on-resistance, thus saving energy. It has been predicted that in some applications the SiC MOSFET will replace the Si-IGBT in the voltage range of more than 1 kV.

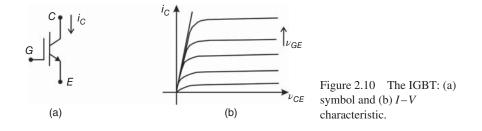

**The IGBT** The IGBT promoted a great revolution in power electronics as it uses a mixed bipolar-MOSFET technology. It combines the advantages of the MOSFET and the BJT Darlington, with controlled turn-on and turn-off. Like the MOSFET it has a high input impedance and needs low energy to be switched on. Its symbol and I-V characteristics are given in Fig. 2.10. The IGBT conduction drop voltage is small (from 2 to 3 V in a device of 1 kV). The conventional device is unidirectional in current and only blocks forward voltage (UniI/UniV) with a voltage of 6.5 kV for 750 A, or 1.7 kV for 3.6 kA for dv/dt of order from 50,000 V/µs to 100,000 V/µs. The type NPT ("nonpunch-through") can reach 3.5 kV and 2 kA. Its typical turn on and turn off time is from 200 ns to 1 µs. It is possible to design it to block the voltage in both directions, forward and reverse voltages. Such a device has been recently introduced in the market with the name of reverse blocking IGBT but for lower voltage (1.7 kV) and current (25 A), 1200 V/40 A, 600 V/200 A. As for the MOSFET, the SiC technology is also designing SiC–IGBT, which has reached the high blocking voltage of 15 kV.

**The GTO** The GTO did appear to give thyristors the option to control its turn-off. Its symbol and I-V characteristics are given in Fig. 2.11 and it is, normally, a UniC/UniV device. For turning on, it only needs a small pulse of positive current at the gate. However, its turn-off current gain of the negative current pulse is typically 3-5, which means that for turning off a 6 kV/6 kA GTO, it needs a negative gate

Figure 2.11 The GTO: (a) symbol and (b) I-V characteristic.

current pulse of 1.5 kA. The reverse blocking GTO can withstand reverse voltage of 4.5 kV with 3 kA. Also, the GTO needs snubbers when used with inductive load.

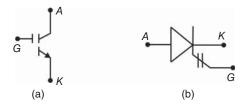

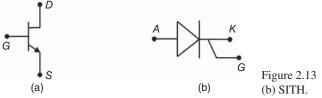

**The MCT** The MCT is also called MOS-GTO and combines the characteristics of the FET integrated with the p-n-p-n structure of a thyristor. It is a UniC/UniV device. When designed, it was expected that it would be able to handle more than 200 kVA and more than 1 MVA in subsequent years. In conduction, it approximates to the SCR characteristics. Its blocking is obtained through the turn-off gate. However, even though it reached values of 2 and 3 kV and hundreds of amperes, its acceptance by the market is still undefined at the moment. Its symbol is given in Fig. 2.12(a).

**The IGCT** The IGCT was introduced in 1997 and it is a high voltage, high power, asymmetric blocking device, with a structure very similar to a GTO thyristor. As it is designed with a monolithically integrated antiparallel diode, it is a BidC/UniV type of device. Its symbol is given in Fig. 2.12(b). It is a device with unity turn-off current gain. This means that a 4.5 kV IGCT with a controllable anode current of 3000 A requires a turn-off negative gate current of 3 kA. So it needs a great amplification for turn off and, also, the gate driver must have an ultralow leakage inductance in order to have short duration and very large di/dt. With this purpose, the gate drive circuit is built in and such integration between the command and the device results in high turn-off speed (1  $\mu$ s) and basically eliminates the problem of dv/dt found in GTOs permitting snubberless operation. In IGCTs the cathode current is diverted to the gate before any distribution of current between gate and anode is observed so that the structure p-n-p-n can be converted to a p-n-p structure. As a result, the IGCT conducts as a GTO but turns off as an IGBT, combining the characteristics of these devices. Other parameters superior in the IGCT as compared to the GTO are the conduction drop voltage and gate-driver loss. Its typical frequency is around 500 Hz it can reach 1 kHz. The device has been applied in power system installations of 100 MVA and medium power (up to 5 MW) industrial drives. Like the GTO and IGCT, the reverse blocking IGCT (RBIGCT), symmetric, has been recently developed, and can withstand 5 kV.

### 2.3.4 Spontaneous Conduction/Controlled Blocking Devices

Two devices can be classified as SC/CB, that is, the static induction transistor (SIT) normally-on and the Static Induction Thyristor (SITH) normally-on.

Figure 2.12 Symbol of the: (a) MCT and (b) IGCT.

Figure 2.13 Symbol of: (a) SIT and (b) SITH.

The SIT The SIT, also known as Junction Field-Effect Transistor (J-FET), is an *n*-type field-effect transistor, voltage driven. Its symbol is given in Fig. 2.13(a). It is a UniC/UniV device with ratings of 1.2 kV and 300 A and can operate up to 100 kHz. It conducts when  $v_{GS} = 0$  and its drain current can be controlled by the gate-source voltage,  $v_{GS}$ . However, the gate-source voltage required for turning off the device is high and it is not uncommon that a voltage as high as 40 V (negative) is needed. This characteristic of normally turned on with controlled turn-off classifies the device as SC/CB (the SIT normally-off has been already developed, with limited performance). However, its high forward voltage makes it unsuitable for most power electronics applications, unless radio frequency operation is needed. Additionally, the difficulty in manufacturing it raises concerns about its mass production. This device has been shown to be more promising with the SiC technology reaching ratings of 1.2 kV/17 Aand 6.5 kV/5 A. Its range of power operation is up to 50 kW. It has been shown that a SiC SIT of 125 V/2.2 kW can operate in the ultrahigh frequency range up to 450 MHz. However, the gate-source voltage required for turning this device off is about  $V_{GS} = -30$  V. Although SiC SIT is a normally-on device, recently a SiC SIT normally-off has been developed with ratings of 1.2 kV and 35 A, with a turn-off  $V_{GS}$ of only -2.5 V.

**The SITH** The SITH, or SIThy, a device unidirectional in voltage, is a combination of an *n*-channel SIT and a p-n-p transistor. Its symbol is given in Fig. 2.13(b). It is a normally-on device with turn-off controlled by negative gate voltages and it does not have reverse blocking capability. It can handle currents in the range of 300 A to 2 kA with a recovery time from 2 to 4 µs and it is a device rated with 1.5 kV/300 A and has a rated frequency of 10 kHz but it is expected to be applied to power sources up to 10 MHz. Although it can operate at higher frequencies compared to the GTO, its higher drop voltage and lower current gain are its main disadvantages. As for the SIT, the complexity of the manufacture process and the high negative gate voltage for turning it off are its major drawbacks.

#### Exercise 2.1

The simple circuit presented below allows the power flow control between the voltage source ( $V_{dc} = 1 \text{ kV}$ ) and the resistive load ( $R_o$ ), by turning-on and -off the switch S with switching frequency equal to  $f_s$ . From the ratings of the

switches given in this chapter determine the appropriate power device to be employed as the switch *S*, considering the following conditions:

(a)  $f_s = 1$  kHz and  $R_o = 0.6$

**(b)**  $f_s = 50$  kHz and  $R_o = 2.5$ **(c)**  $f_s = 200$  kHz and  $R_o = 10$ .

## 2.3.5 List of Inventors of the Major Power Switches

The list of inventors of the major power devices available in today's market is presented here:

- *Diode pn*. The first semiconductor diode, a germanium-made device, was created in 1952, 200 V/35 A, by R.N. Hall. Its counterpart in silicon was invented by Russell Ohl at Bell Laboratories, 500 V.

- *BJT*. In 1947, W. Shockley, J. Bardeen, and W. Brattain built a germanium point-contact transistor. The BJT was created by W. Shockley from Bell Laboratory in 1948 and developed in 1950 for 500 V/20 A. The first commercially available silicon devices (grown junction) were manufactured in 1954 by Gordon Teal.

- *SCR (Thyristor).* The SCR or thyristor was proposed by William Shockley in 1950. It was theoretically described in 1954 and 1955 by J.L. Moll from Bell Laboratory but it was not well accepted until GE manufactured a feasible device in 1957. Its commercial version was available in 1958 and was championed by G. E.'s Frank W. "Bill" Gutzwiller (300 V/16 A).

- *GTO*. The GTO thyristor was created in 1962 by R. Aldrich and N. Holonyak from GE. It was used until the 1970s when it was replaced by the silicon power MOSFET and IGBT. This happened because the GTO was limited to low current. For instance, in 1967 its maximum rates were 500 V/10 A. However, an improved Hitachi GTO was developed in 1981 allowing for higher voltage and current (2500 V/1000 A).

- *TRIAC*. The bidirectional triode thyristor was created by F. W. Gutzwiller, from GE, in 1963. It reached 40 A experimentally but the first commercial Triacs were the SC40 and SC45, rated 200 V, 6 A, and 10 A, in 1965 and 1966, respectively, following basic research steps developed by GE's Aldrich and Nick Holonyak (1958), and Finis E. Gentry and Tuft (1963).

- RCT. The RCT was created in 1970 by Kokosa and B. Tuft from GE.

- *MOSFET*. The first metal-oxide field-effect transistor was created in 1958 and reported in 1960 by D. Kahng and M.M. Atalla, from Bell Laboratory. However, the first successfully commercialized power MOSFET was from International Rectifier.

- *SITH or FCT (Field-Controlled Thyristor).* The SITH was proposed by J. Nishizawa from Mitsubishi Electric Corporation in 1975 (700 V); in the same year a similar device that received the name of FCT was reported by D.E. Houston.

- *IGBT*. The first IGBT with substantial current ratings was developed in 1982 by J. Baliga, from GE, with a symmetric blocking voltage of 600 V for 10 A (6 kVA). It was also reported by J.P. Russel in 1983 under the name of COM-FET, reaching 400 V and 30 A.

- SIT (normally "on" or JFET) was introduced by J. Nishizawa in 1975, 300 V, 2 A, with an output power of 5 W at 1 GHz, 36W at 200 kHz and 40 W at 100 MHz.

- *BCT*. The bilateral controlled thyristor was created by ABB in 1998, having voltage and current ratings of 6.5 kV and 1390 A.

- *IGCT*. The IGCT was conceived in 1993 at ABB and reported in 1996 by P.K. Steimer, H. Gruning et al. from ABB for 4.5 kV and 3 kA. It was also reported in 1996 by J. Sakano et al. from Hitachi and was able to block 4 kV.

- *MTO*. The MOS turn-off thyristor was invented in 1995 by D.E. Piccone et al. from Silicon Power Corporation, with rated values of 6000 V and 500 A.

## 2.4 BASIC CONVERTERS

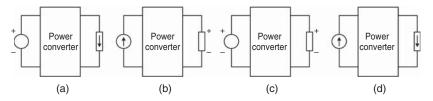

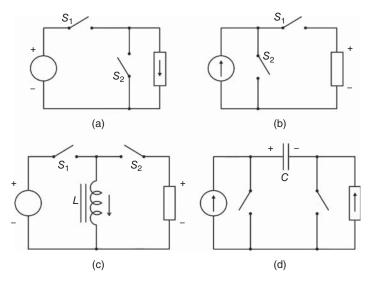

As mentioned earlier, a power electronics converter interfaces a source and a load (or another source). The source can be either of voltage type or current type. Also, the load can be of either voltage type (e.g., a capacitive load) or current type (e.g., an inductive load). The connection between a source and a load should obey the following sequences: (i) *voltage* (*V*)-*current* (*I*)-*voltage* (*V*)-*current* (*I*), or (ii) *current* (*I*)-*voltage* (*V*)-*current* (*I*)-*voltage* (*V*). Four connections between source and load are then possible, as shown in Fig. 2.14, which establishes the following connections, V-I, I-V, V-V and I-I. Notice that, for the V-V connection as in Fig. 2.14(c), the power converter interfacing load and source are expected

Figure 2.14 Four possibilities of connection between source and load.

to have an inductor element inside that block. The same rationale applies for Fig. 2.14(d).

Only sources and loads of different types can be directly connected, that is: (i) a voltage source can be directly connected to a current-type load and (ii) a current source can be directly connected to a voltage-type load. Such a restriction comes from the need to avoid, for example, a parallel connection between two voltage-type elements, and so preventing short-circuit between these two elements.

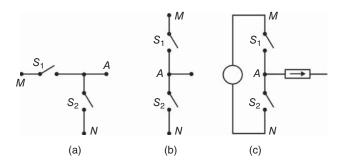

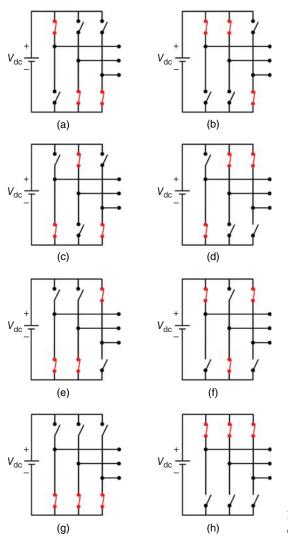

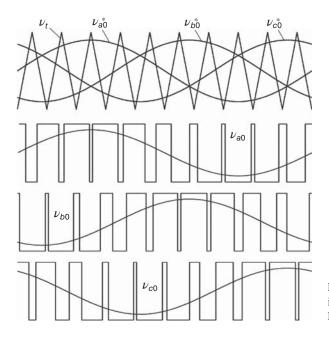

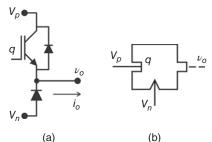

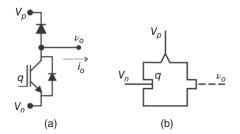

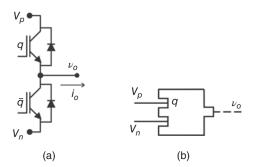

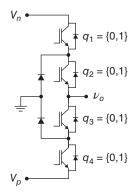

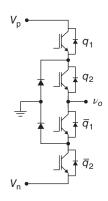

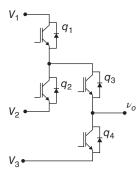

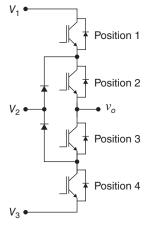

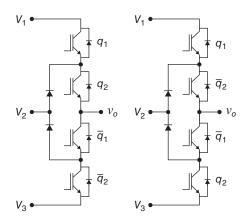

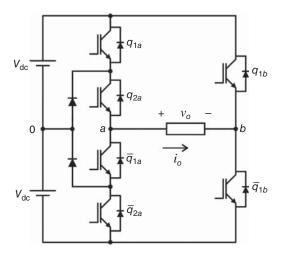

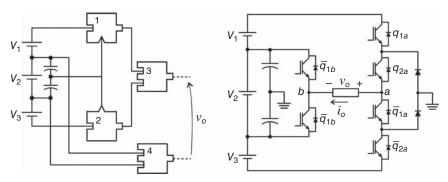

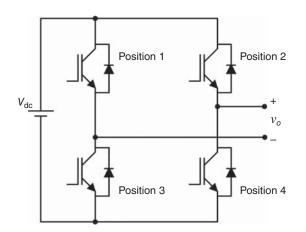

Except for the case of resistive load, the minimal number of switches that allows interconnecting a source and a load is two, which is called basic commutation cell. In fact such a commutation cell can be obtained with two different arrangements, as seen in Figs 2.15 (Cell I) and 2.16 (Cell II). Cell I in Fig. 2.15(a), also known as leg when it is arranged as presented in Fig. 2.15(b), can be used to connect a voltage source to an inductive load. In Fig. 2.15(c), the source is connected between points M and N while the load is connected to the point A, named as pole. Instead, in Cell II in Fig. 2.16(a), or its leg representation [Fig. 2.16(b)], the current source connected to point A allows feeding a capacitive load connected between points M and N (voltage-type load), as shown in Fig. 2.16(c). It should be noticed that while one of the switches is conducting, the other one is turned off. Note that the pole (point A) can be connected to either point M or point N, so that it can only assume the potential of those points. For this reason, both cells are said to be two-level cells.

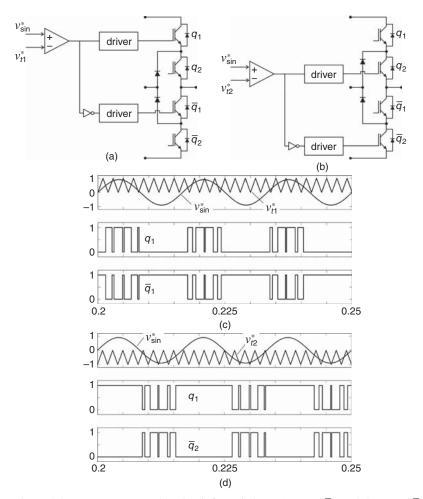

Figure 2.15 Basic cell employed to connect voltage source to current-type load.

Figure 2.16 Basic cell employed to connect current source to voltage-type load.

Figure 2.17 Principles for building power converters.

Figure 2.17 shows how different types of sources and loads can be connected through the basic cells presented in Figs 2.15 and 2.16. As mentioned earlier, sources and loads of the same type can only be connected through an intermediate coupling circuit. For example, to connect a voltage source to a voltage-type load, it is necessary to employ a current-type element (inductor) between the source and load [see Fig. 2.17(c)]. For duality, the voltage-type element is a capacitor that is used to connect both current source and current-type load, as shown in Fig. 2.17(d).

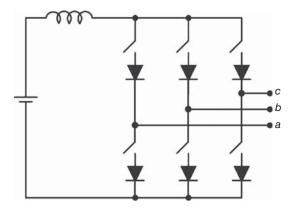

The basic cells permit the basic converters used to convert energy from dc-to-dc, dc-to-ac, ac-to-dc, and ac-to-ac (or simply dc-dc, dc-ac, ac-dc, and ac-ac) and also to extend them to more complex structures, in a more systematic way. This will be in fact the approach employed in this book.

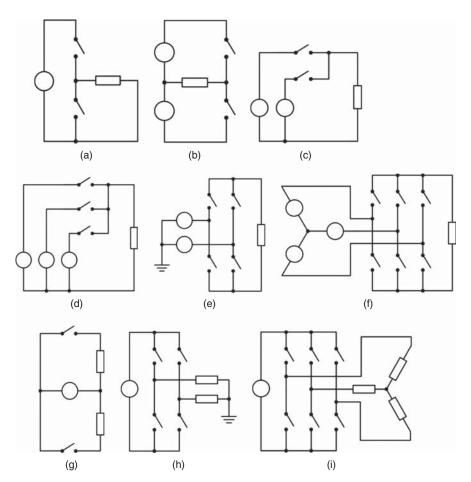

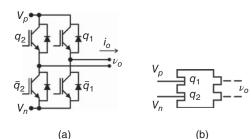

Depending of the application, it is possible to define two scenarios: (i) one load supplied by one or more sources and (ii) one source supplying one or more loads. Consider first the case in which there is only one load supplied from one or more sources. Each source can be connected to either a switch (corresponding to the point *M* in Fig. 2.15, for example), as shown in Fig. 2.18(a)–2.18(d), or to the pole (midpoint of the leg, i.e., point *A*), as shown in Fig. 2.18(e) and 2.18(f). Similarly, for the second scenario, when there is only one source and the load is constituted by one or more elements, each part of the load can be connected to either a switch (point *M*, for example), as shown in Fig. 2.19(g) or to the midpoint of the leg (*A*), as shown in Fig. 2.18(h) and 2.18(i).

Notice from Figs 2.15–2.18 that the power switches, sources, and loads are represented generically. The procedure to choose first the appropriate power switch and the converter with desirable characteristics depends on the type of source and load that have been considered, as well as the requirements for a specific application.

Figure 2.18 Different ways to connect source(s) to the load(s).

The following technical characteristics are used for choosing the appropriate switch and converter: (i) UniC or BidC, (ii) UniV or BidV, (iii) SC or CC, and (iv) SB or CB. Other essential features are switching frequency, voltage and current ratings, and cost.

## 2.4.1 dc-dc Conversion

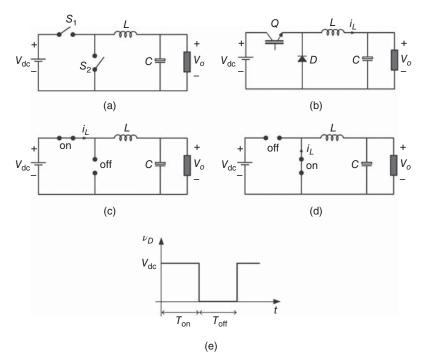

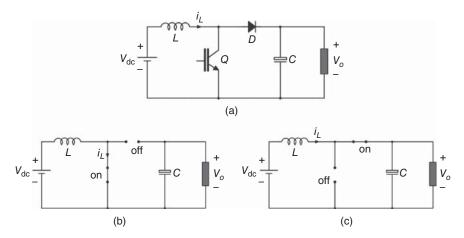

**Buck Converter** The buck converter is presented in Fig. 2.19(a), which comprises (i) a dc voltage source  $(V_{dc})$ , (ii) a basic cell as in Fig. 2.15(a) with switches  $S_1$  and  $S_2$ , (iii) energy storage component (*L*) due to the interface between two voltage-type elements, and (iv) a resistive load with voltage  $V_o$ . As demanded for this application, both switches  $S_1$  and  $S_2$  should be (a) UniC and UniV and (b) CC and CB. However, notice that  $S_2$  must be complementary to  $S_1$  to avoid a short circuit of the dc source ( $V_{dc}$ ), which means that when  $S_1$  is on,  $S_2$  should be off, and when  $S_2$  is on,  $S_1$  should be off.

Figure 2.19 Buck converter with: (a) basic cell and (b) real switches. (c) TS 1. (d) TS 2. (e) Diode voltage.

This means that the circuit will have the same functionality if a SC/SB type of switch (i.e., diode) is employed for  $S_2$ . Then, the circuit will be as shown in Fig. 2.19(b).

There are two topological states (TSs) for the buck converter:

- TS 1—The switch Q is on and conducts the inductor current, while the diode is off, as shown in Fig. 2.19(c).

- TS 2—When Q is turned off, the diode conducts the inductor current, as shown in Fig. 2.19(d).

## Example 2.1

Explain why a buck converter such as the one presented in Fig. 2.19 requires two power switches with UniC and UniV characteristics.

### Solution

As the output voltage is dc, the load current is also dc, which leads to a dc current for  $I_L$ . During the TS 1, the switch Q will carry this unidirectional type of current (UniC) and during the TS 2 the diode will carry  $I_L$ . When both

switches are turned off their current will be zero. In terms of the voltage applied to those devices, it is also UniV, as the voltage will be either zero or  $V_{dc}$  for Q and either zero or  $-V_{dc}$  for D.

Figure 2.19(e) shows the diode voltage, which is the voltage applied to the *LC* filter. While the time domain representation—as in Fig. 2.19(e)—provides a good understanding of the topology itself, the frequency domain with the Fourier series allows identification of the frequency components. In general terms, the expansion of a periodical waveform f(t) in Fourier series is given by

$$f(t) = F_o + \sum_{n=1}^{\infty} f_n(t) = \frac{1}{2}a_o + \sum_{n=1}^{\infty} \{a_n \cos(n\omega t) + b_n \sin(n\omega t)\}$$

(2.1)

where  $F_o = 1/2(a_o)$  is the average value and

$$a_n = \frac{1}{\pi} \int_0^{2\pi} f(t) \cos(n\omega t) d(\omega t) \quad \text{for } n = 0, \dots, \infty$$

(2.2)

$$b_n = \frac{1}{\pi} \int_0^{2\pi} f(t) \sin(n\omega t) d(\omega t) \quad \text{for } n = 1, \dots, \infty$$

(2.3)

In the case of Fig. 2.19(e), the average value  $F_o$  in (2.1) is given by

$$V_o = \frac{T_{\rm on} V_{\rm dc}}{T_s} = dV_{\rm dc} \text{ with } d = T_{\rm on}/T_s$$

(2.4)

where  $T_{on}$  is the interval of time with the switch  $S_1$  on,  $T_s$  is the switching period  $(T_{on} + T_{off})$ , and *d* is known as duty cycle.

Notice that the input voltage of the *LC* filter has infinite components of frequency [see equation (2.1)], which must be filtered allowing, ideally, an output voltage  $V_o$  with only the zero frequency component, as in equation (2.4).

## Example 2.2

Assume the inductor voltage waveform and the information that this energy storage component is in fact a passive element to deduce equation (2.4) without the expansion in Fourier series.

#### Solution

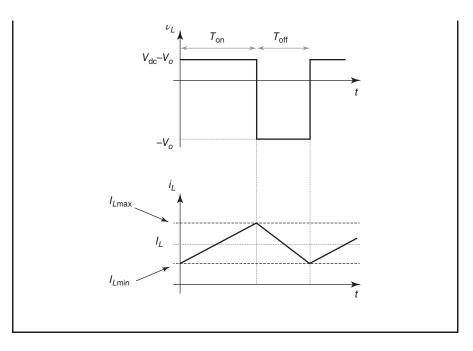

The graphs below show the inductor waveforms (voltage and current) assuming a continuous conduction mode (i.e.,  $i_L$  is always higher than zero). As the inductor is a passive component, the average power on this device is zero, leading to an average voltage also equal to zero. It turns out that: $(V_{dc} - V_o)T_{on} = V_o T_{off}$  and consequently:  $V_o/V_{dc} = T_{on}/T = d$ .

## Exercise 2.2

By using equations (2.2) and (2.3) calculate the Fourier coefficients  $a_n$  and  $b_n$  from 0 to the seventh harmonic for two waveforms of the diode voltage with buck converter operating with d = 0.5 and 0.75. Also, consider a switching frequency equal to 50 kHz. If the LC filter in Fig. 2.19 is designed with a cut frequency equal to 20 kHz (3dB), find out if this filter can cut the switching frequency of the buck converter for both cases: d = 0.5 and 0.75?

**Boost Converter** The boost converter with the representation of the real semiconductor devices is presented in Fig. 2.20(a). Its TSs are given in Fig. 2.20(b) and 2.20(c).

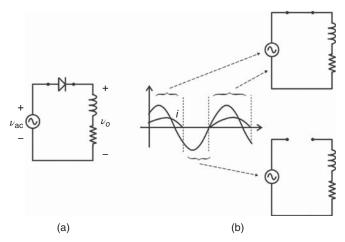

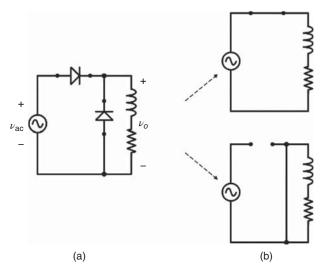

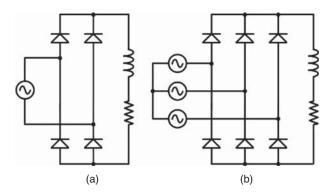

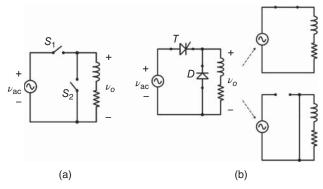

- TS 1—In this mode, the switch is on and the diode is off. The input voltage is then applied to the inductor with a consequent increase in its current  $i_L$ . Since *D* is off, the load current is provided by the capacitor *C*.